High-level synthesis (HLS) automates the translation of algorithmic descriptions into hardware designs, significantly accelerating the development process compared to traditional Register Transfer Level (RTL) design. HLS enables engineers to work with higher abstraction languages like C or SystemC, improving productivity and allowing easier design space exploration. In contrast, RTL design requires manual coding of hardware behavior in languages such as Verilog or VHDL, offering more granular control but increasing development time and complexity.

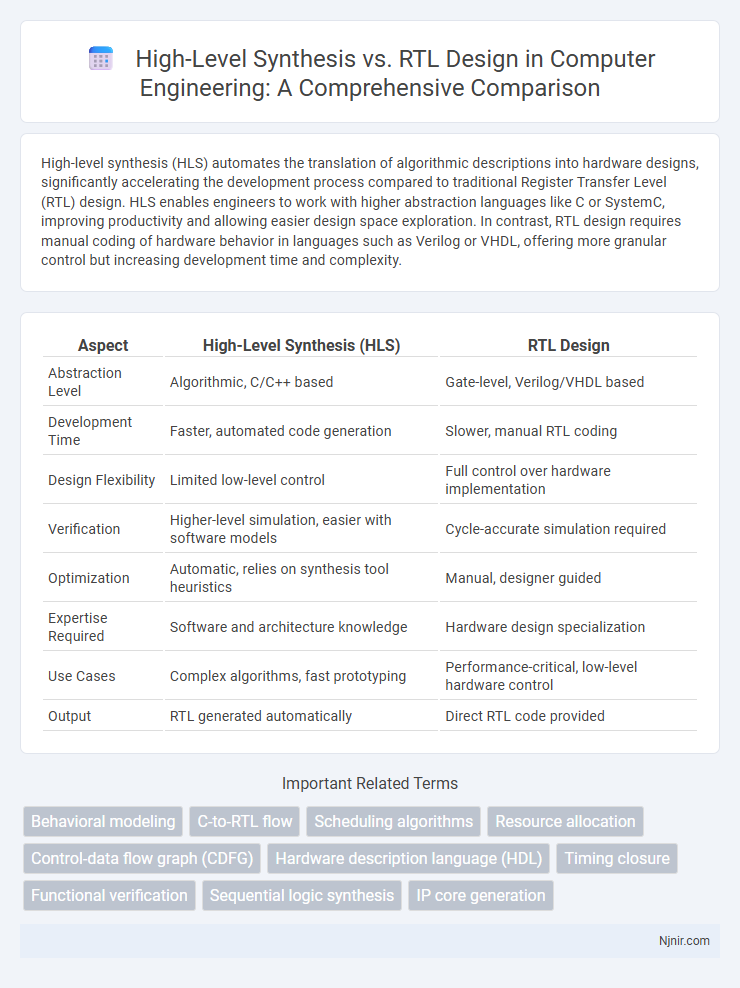

Table of Comparison

| Aspect | High-Level Synthesis (HLS) | RTL Design |

|---|---|---|

| Abstraction Level | Algorithmic, C/C++ based | Gate-level, Verilog/VHDL based |

| Development Time | Faster, automated code generation | Slower, manual RTL coding |

| Design Flexibility | Limited low-level control | Full control over hardware implementation |

| Verification | Higher-level simulation, easier with software models | Cycle-accurate simulation required |

| Optimization | Automatic, relies on synthesis tool heuristics | Manual, designer guided |

| Expertise Required | Software and architecture knowledge | Hardware design specialization |

| Use Cases | Complex algorithms, fast prototyping | Performance-critical, low-level hardware control |

| Output | RTL generated automatically | Direct RTL code provided |

Introduction to High-Level Synthesis and RTL Design

High-Level Synthesis (HLS) transforms algorithmic C/C++ descriptions into Register Transfer Level (RTL) code, enabling faster design space exploration and shorter development cycles. Register Transfer Level design involves writing detailed hardware descriptions in languages like VHDL or Verilog, providing precise control over hardware behavior and timing. HLS abstracts lower-level hardware details, improving productivity, while RTL design offers fine-grained control crucial for optimizing performance and resource utilization.

Fundamental Differences between HLS and RTL

High-level synthesis (HLS) translates algorithmic descriptions written in languages like C/C++ into register-transfer level (RTL) code, enabling designers to work at a higher abstraction level compared to traditional RTL design, which involves manual coding in hardware description languages such as Verilog or VHDL. HLS emphasizes automation, allowing for rapid prototyping and early design space exploration, whereas RTL design provides granular control over hardware implementation, timing, and resource optimization. The fundamental difference lies in abstraction level and design methodology: HLS abstracts hardware details to accelerate development, while RTL offers precise, cycle-accurate control essential for performance-critical applications.

Design Abstraction Levels in HLS and RTL

High-level synthesis (HLS) operates at a higher design abstraction level by transforming algorithmic descriptions in languages like C/C++ into hardware description language (HDL) code, allowing designers to focus on functionality rather than hardware details. RTL design, on the other hand, works at a lower abstraction level, specifying exact register transfer operations and cycle-accurate hardware behavior using HDLs like Verilog or VHDL. The abstraction level in HLS enables faster design space exploration and productivity gains, while RTL provides fine-grained control over timing and resource optimization.

Workflow and Methodology Comparison

High-level synthesis (HLS) automates the translation of algorithmic descriptions written in languages like C/C++ into RTL code, significantly accelerating the design workflow by enabling early verification and rapid iterations. RTL design requires manual coding of hardware description languages such as Verilog or VHDL, emphasizing detailed control and timing precision but often resulting in longer development cycles. HLS methodology optimizes complex designs through automated scheduling and resource allocation, while traditional RTL design relies on designer expertise for low-level optimizations and structural definition.

Toolchains and Language Support

High-level synthesis (HLS) toolchains translate algorithms written in languages like C, C++, or SystemC into Register Transfer Level (RTL) code, enabling faster design space exploration and increased productivity. RTL design toolchains primarily support hardware description languages such as Verilog and VHDL, offering fine-grained control over hardware implementation but requiring more manual effort. HLS tools integrate with simulation and verification environments to automate optimization, while RTL design remains heavily dependent on traditional synthesis, place-and-route, and timing analysis flows.

Design Productivity and Time-to-Market

High-level synthesis (HLS) significantly enhances design productivity by automating the translation of algorithmic descriptions into hardware, reducing manual coding errors and iteration cycles compared to traditional RTL design. HLS accelerates time-to-market by enabling faster prototyping and early software-hardware co-design, cutting development timelines by weeks or months. RTL design, while offering precise control and optimization, typically demands more engineering effort and longer development times, impacting overall project schedules.

Quality of Results: Performance and Area Trade-offs

High-level synthesis (HLS) offers automated optimization techniques that can improve design productivity while achieving competitive Quality of Results (QoR) in terms of performance and area trade-offs compared to traditional Register Transfer Level (RTL) design. HLS allows designers to explore multiple architectural choices rapidly, enabling better balancing of timing constraints and resource utilization, which can lead to enhanced performance with reduced silicon area. However, RTL design provides finer control and predictability, often resulting in more optimized implementations for critical paths, but at the cost of increased development time and complexity.

Debugging and Verification Approaches

High-level synthesis (HLS) enables quicker debugging through algorithmic-level simulations and formal verification techniques that abstract away low-level hardware details, streamlining the identification of design flaws early in the development cycle. RTL design debugging relies heavily on waveform analysis and hardware description language (HDL) simulators, which provide cycle-accurate insights but demand more effort and time to trace errors at the gate level. Verification in HLS often leverages automated testbench generation and assertion checking, while RTL verification uses constrained random testing and coverage-driven methodologies to ensure exhaustive validation of hardware behavior.

Application Suitability and Use Cases

High-level synthesis (HLS) excels in complex algorithmic designs, enabling rapid prototyping and design space exploration in AI, machine learning, and data processing applications. RTL design remains the preferred choice for applications demanding precise timing control, high performance, and fine-grained hardware optimization such as embedded systems and custom processor cores. HLS suits early-stage development and innovation cycles, while RTL design targets mature products requiring deterministic behavior and resource-efficient implementation.

Future Trends in HLS and RTL Design

Future trends in high-level synthesis (HLS) emphasize increased automation, AI-driven optimizations, and enhanced integration with system-level design tools to accelerate hardware development cycles. RTL design continues to evolve with improved verification methods, machine learning-assisted bug detection, and higher abstraction layers to manage growing design complexity. Both HLS and RTL are converging towards hybrid workflows that leverage the strengths of synthesis automation and low-level control to optimize performance, power, and area in next-generation semiconductor technologies.

Behavioral modeling

High-level synthesis leverages behavioral modeling to automatically generate RTL code from abstract algorithmic descriptions, significantly accelerating design cycles compared to manual RTL design.

C-to-RTL flow

C-to-RTL flow in high-level synthesis enables automatic generation of Register Transfer Level code from C/C++ source, significantly accelerating hardware design compared to manual RTL design.

Scheduling algorithms

Scheduling algorithms in high-level synthesis optimize operation timing and resource allocation automatically, whereas RTL design requires manual scheduling and precise control of hardware timing.

Resource allocation

High-level synthesis optimizes resource allocation by automatically mapping algorithms to hardware components, while RTL design requires manual resource scheduling and precise control over hardware utilization.

Control-data flow graph (CDFG)

Control-data flow graph (CDFG) in high-level synthesis abstracts and optimizes complex control and data dependencies for efficient hardware implementation, whereas RTL design directly describes circuit-level timing and structure without inherent CDFG representation.

Hardware description language (HDL)

High-level synthesis (HLS) automates hardware design by converting high-level programming languages like C/C++ into Hardware Description Language (HDL) code, whereas RTL design requires manual coding directly in HDL languages such as VHDL or Verilog for precise hardware circuit specification.

Timing closure

High-level synthesis accelerates timing closure by enabling early design space exploration and automated optimization, while RTL design requires manual timing adjustments and iterative refinements to meet timing constraints.

Functional verification

Functional verification in high-level synthesis dramatically reduces verification time by enabling early bug detection through higher abstraction models compared to the cycle-accurate, time-consuming RTL design verification process.

Sequential logic synthesis

High-level synthesis automates sequential logic synthesis by converting algorithmic descriptions into hardware, significantly improving design productivity and enabling rapid exploration compared to traditional RTL design which requires manual, cycle-accurate coding of sequential circuits.

IP core generation

High-level synthesis accelerates IP core generation by converting algorithmic descriptions into optimized RTL code, enhancing design abstraction and reducing development time compared to manual RTL design.

high-level synthesis vs RTL design Infographic

njnir.com

njnir.com