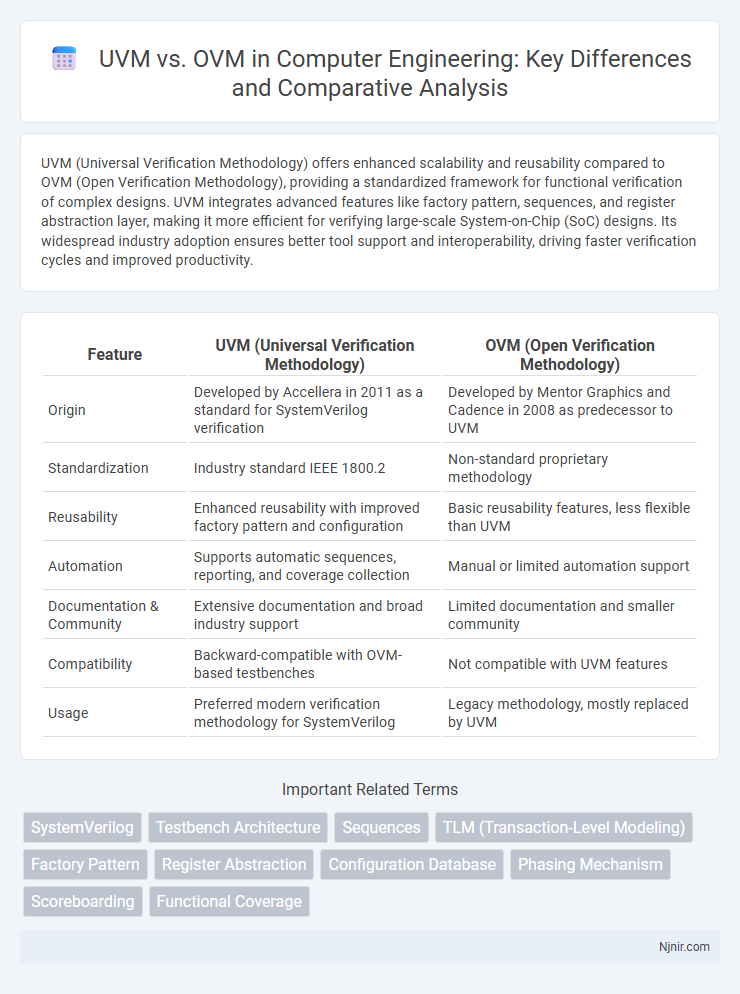

UVM (Universal Verification Methodology) offers enhanced scalability and reusability compared to OVM (Open Verification Methodology), providing a standardized framework for functional verification of complex designs. UVM integrates advanced features like factory pattern, sequences, and register abstraction layer, making it more efficient for verifying large-scale System-on-Chip (SoC) designs. Its widespread industry adoption ensures better tool support and interoperability, driving faster verification cycles and improved productivity.

Table of Comparison

| Feature | UVM (Universal Verification Methodology) | OVM (Open Verification Methodology) |

|---|---|---|

| Origin | Developed by Accellera in 2011 as a standard for SystemVerilog verification | Developed by Mentor Graphics and Cadence in 2008 as predecessor to UVM |

| Standardization | Industry standard IEEE 1800.2 | Non-standard proprietary methodology |

| Reusability | Enhanced reusability with improved factory pattern and configuration | Basic reusability features, less flexible than UVM |

| Automation | Supports automatic sequences, reporting, and coverage collection | Manual or limited automation support |

| Documentation & Community | Extensive documentation and broad industry support | Limited documentation and smaller community |

| Compatibility | Backward-compatible with OVM-based testbenches | Not compatible with UVM features |

| Usage | Preferred modern verification methodology for SystemVerilog | Legacy methodology, mostly replaced by UVM |

Introduction to UVM and OVM

UVM (Universal Verification Methodology) and OVM (Open Verification Methodology) are standardized methodologies for functional verification of integrated circuits, widely used in the semiconductor industry. UVM, developed by Accellera, builds upon OVM by enhancing reusability, scalability, and automation capabilities, enabling more efficient testbench creation for complex designs. OVM, initially created by Mentor Graphics and Cadence, laid the foundation for modern verification flows through its object-oriented approach and modular architecture.

Historical Background and Evolution

UVM (Universal Verification Methodology) evolved from OVM (Open Verification Methodology), addressing limitations in scalability and reusability within complex SoC verification environments. OVM was developed collaboratively by Cadence and Mentor Graphics as a unified approach combining previous methodologies (VMM and OVM origins) to standardize verification processes. UVM built on OVM's foundation by integrating IEEE standardization efforts, introducing a comprehensive base class library and enhanced capabilities for modular and scalable testbench architecture.

Key Concepts of UVM

Universal Verification Methodology (UVM) enhances OVM by introducing advanced features such as factory patterns, improved phasing, and a standardized reporting mechanism, which optimize reusability and scalability in testbench development. Key concepts of UVM include sequences for stimulus generation, transaction-level modeling to abstract communication, and a comprehensive register model to ensure efficient hardware-software verification. Its modular architecture supports layered verification components like drivers, monitors, and scoreboards, enabling robust and automated verification environments for complex System-on-Chip (SoC) designs.

Key Concepts of OVM

OVM (Open Verification Methodology) centers on key concepts such as layered verification architecture, reusable components, and a standardized base class library that facilitates efficient functional verification. It emphasizes modularity with entities like drivers, monitors, scoreboards, and sequencers, promoting easy integration and scalable testbench development. Unlike UVM, OVM focuses on simplicity and rapid adoption while providing a foundation for advanced verification strategies.

Architecture Comparison: UVM vs OVM

UVM (Universal Verification Methodology) enhances OVM (Open Verification Methodology) by introducing a more standardized and modular architecture, improving reusability and scalability in verification environments. UVM integrates a layered class library with a factory pattern, configuration mechanism, and a transaction-level modeling approach, enabling more efficient testbench construction and management compared to OVM's simpler framework. The adoption of UVM's advanced reporting, phased execution, and analysis components offers greater flexibility and control over simulation processes versus OVM's less comprehensive architectural features.

Feature Differences Between UVM and OVM

UVM (Universal Verification Methodology) introduces standardized transaction-level modeling and enhanced factory patterns compared to OVM (Open Verification Methodology), enabling more scalable and reusable testbenches. UVM supports advanced phasing mechanisms and improved reporting features that offer finer control over simulation flow and debugging capabilities. It also integrates built-in support for sequence items and communication mechanisms, which enhances stimulus generation and response checking beyond OVM's capabilities.

Industry Adoption and Ecosystem Support

UVM (Universal Verification Methodology) has become the industry standard widely adopted by semiconductor companies and design verification teams due to its standardized base class library and strong support from Accellera and major EDA vendors. In contrast, OVM (Open Verification Methodology), while influential in shaping UVM, saw limited long-term adoption and has largely been phased out in favor of UVM's more comprehensive ecosystem and broader community support. The robust UVM ecosystem includes extensive verification IP, training resources, and tool interoperability, driving faster integration and higher productivity across complex SoC verification projects.

Migration Challenges: OVM to UVM

Migrating from OVM to UVM presents challenges such as differences in methodology structure, class libraries, and phasing mechanisms that require extensive code refactoring and validation. Verification engineers must address compatibility issues, update testbenches to leverage UVM's standardized components, and adapt to new reporting and configuration interfaces. Effective migration demands thorough training and tool support to minimize integration risks and ensure seamless transition to UVM's advanced verification features.

Best Practices for Testbench Development

UVM (Universal Verification Methodology) offers standardized base classes and factory mechanisms that promote modular and reusable testbench components, enhancing scalability over OVM (Open Verification Methodology). Best practices recommend leveraging UVM's transaction-level modeling and constrained random stimulus to improve coverage and test efficiency. Implementing consistent phasing and layered architecture ensures clear synchronization and easier maintenance compared to OVM-based environments.

Future Trends in Verification Methodologies

UVM (Universal Verification Methodology) is rapidly evolving to incorporate SystemVerilog enhancements and support for advanced coverage-driven verification techniques, surpassing the foundational OVM (Open Verification Methodology). Future trends emphasize increased adoption of machine learning algorithms for predictive analytics in verification, greater integration with hardware emulation platforms, and improved support for portable stimulus standards to boost reuse and scalability. Verification methodologies are increasingly focusing on automation, standardization, and cross-platform interoperability to address the complexities of modern SoC designs.

SystemVerilog

UVM enhances SystemVerilog testbench architecture by offering standardized, reusable verification components and methodology improvements over OVM for scalable, efficient verification.

Testbench Architecture

UVM testbench architecture enhances modularity and scalability with advanced factory mechanisms and phased execution compared to OVM's simpler, less flexible structure.

Sequences

UVM sequences offer enhanced flexibility, improved synchronization, and advanced phasing mechanisms compared to OVM sequences, enabling more efficient and reusable testbench stimulus generation.

TLM (Transaction-Level Modeling)

UVM enhances TLM by providing standardized, reusable communication interfaces and improved abstraction layers compared to OVM, enabling more efficient transaction-level modeling and scalable testbench architectures.

Factory Pattern

UVM enhances the Factory Pattern by providing a more flexible and scalable mechanism for object creation and configuration compared to OVM, enabling improved reuse and testbench customization.

Register Abstraction

UVM offers an enhanced Register Abstraction Layer compared to OVM, providing standardized, reusable, and configurable register models for efficient verification of complex SoC designs.

Configuration Database

UVM's Configuration Database provides a more flexible, hierarchical, and standardized approach for managing configuration parameters across testbench components compared to OVM's less structured mechanism.

Phasing Mechanism

UVM's phasing mechanism extends and refines OVM's by introducing standardized pre and post phases with improved synchronization and flexibility for complex testbench timing control.

Scoreboarding

UVM scoreboarding enhances testbench automation with built-in coverage and analysis features, providing more standardized and reusable verification components compared to OVM's basic scoreboarding capabilities.

Functional Coverage

UVM offers enhanced functional coverage features compared to OVM, including improved coverage group management, advanced cross-coverage capabilities, and built-in coverage configuration mechanisms for more accurate and efficient verification.

UVM vs OVM Infographic

njnir.com

njnir.com