RISC-V offers an open-source, highly customizable instruction set architecture, enabling rapid innovation and flexibility in design, whereas MIPS is a proprietary architecture with a more established ecosystem. RISC-V has gained traction for its modular approach, allowing developers to tailor extensions to specific applications, contrasting with MIPS's fixed instruction formats. The growing industry adoption of RISC-V enhances its ecosystem, making it a compelling choice for future-proof computer engineering projects compared to the traditionally stable but less flexible MIPS architecture.

Table of Comparison

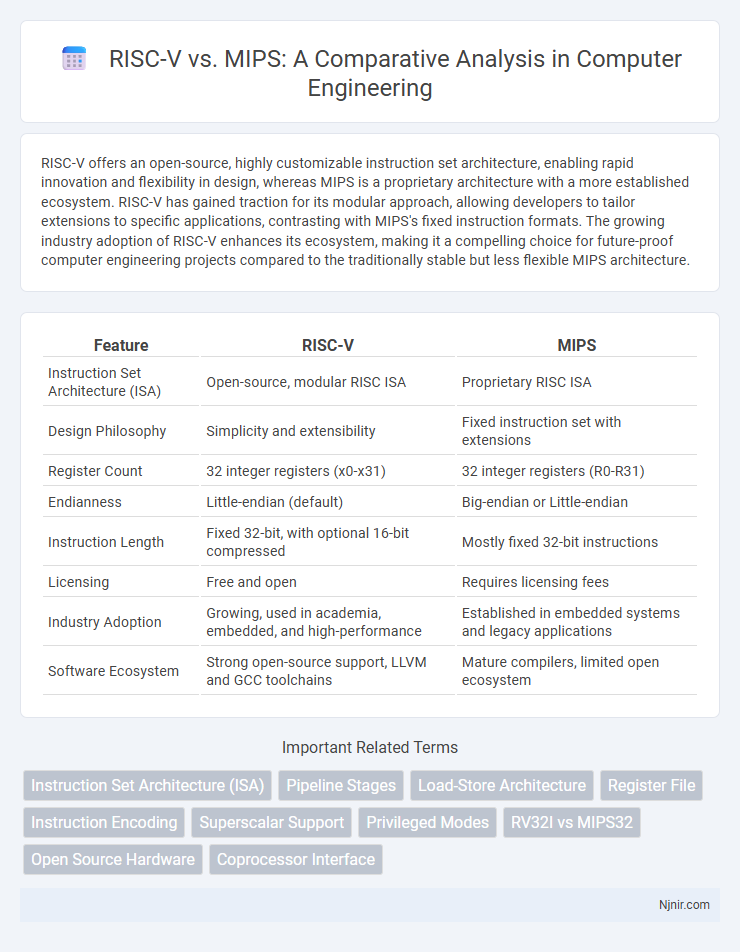

| Feature | RISC-V | MIPS |

|---|---|---|

| Instruction Set Architecture (ISA) | Open-source, modular RISC ISA | Proprietary RISC ISA |

| Design Philosophy | Simplicity and extensibility | Fixed instruction set with extensions |

| Register Count | 32 integer registers (x0-x31) | 32 integer registers (R0-R31) |

| Endianness | Little-endian (default) | Big-endian or Little-endian |

| Instruction Length | Fixed 32-bit, with optional 16-bit compressed | Mostly fixed 32-bit instructions |

| Licensing | Free and open | Requires licensing fees |

| Industry Adoption | Growing, used in academia, embedded, and high-performance | Established in embedded systems and legacy applications |

| Software Ecosystem | Strong open-source support, LLVM and GCC toolchains | Mature compilers, limited open ecosystem |

Introduction to RISC-V and MIPS Architectures

RISC-V architecture is an open-standard Instruction Set Architecture (ISA) designed for simplicity and scalability, supporting both 32-bit and 64-bit environments, enabling widespread adoption in academia and industry. MIPS, established in the 1980s, is a Reduced Instruction Set Computing (RISC) architecture known for its fixed instruction length and load/store design, widely used in embedded systems and networking hardware. Both architectures emphasize efficient instruction execution and pipeline processing, but RISC-V offers modular extensibility and open-source flexibility compared to the proprietary nature of MIPS.

Historical Development and Evolution

RISC-V originated in 2010 at UC Berkeley as an open-source, modular instruction set architecture designed to address limitations of proprietary ISAs like MIPS, which was first developed in the early 1980s by MIPS Computer Systems. MIPS gained widespread adoption in embedded systems and early workstations but faced stagnation due to licensing constraints and competition from ARM and x86 architectures. In contrast, RISC-V's open licensing and scalable design foster rapid innovation and expansion across academia, industry, and emerging applications, marking a significant evolution in processor architecture development.

Instruction Set Architecture Comparison

RISC-V features a modular, open-source Instruction Set Architecture (ISA) designed for extensibility and simplicity, enabling easy customization for various applications, whereas MIPS utilizes a closed ISA with fixed instruction formats primarily optimized for high-performance embedded systems. RISC-V supports a base integer instruction set with optional extension modules for floating-point, atomic, and compressed instructions, promoting adaptability across diverse hardware platforms; MIPS offers a more rigid instruction set structure with a limited range of extensions focused on legacy compatibility. The open governance of RISC-V fosters rapid innovation and widespread adoption, contrasting with MIPS' proprietary model, which restricts modifications and influences its usage in academic and commercial environments.

Design Philosophy: Openness vs Proprietary

RISC-V embraces an open-source instruction set architecture (ISA) that enables unrestricted customization and innovation across hardware designs, fostering a collaborative ecosystem. MIPS follows a proprietary ISA model, which limits access and modifications to licensed users, resulting in restricted flexibility and slower evolution. The openness of RISC-V promotes scalability and adaptability in diverse applications, while MIPS relies on controlled development within its established framework.

Performance and Efficiency Metrics

RISC-V architecture offers superior performance scalability and energy efficiency compared to MIPS, attributed to its modular ISA design and extensive support for custom extensions that optimize processor pipelines. Benchmark analyses reveal RISC-V cores outperform MIPS counterparts in IPC (Instructions Per Cycle) and power consumption metrics, especially in embedded and IoT applications. The open-source nature of RISC-V enables rapid innovation and tailored optimizations, enhancing both throughput and power efficiency over the traditionally proprietary MIPS architecture.

Hardware Implementation and Flexibility

RISC-V offers a highly modular hardware implementation with a base integer ISA and numerous optional extensions, enabling tailored processor designs for diverse applications. MIPS architecture features a more rigid hardware pipeline and fixed instruction set, limiting customization but providing proven stability and efficiency in embedded systems. RISC-V's open standard fosters innovation and flexibility, while MIPS relies on established legacy support and optimized silicon for performance consistency.

Ecosystem and Toolchain Support

RISC-V offers a rapidly expanding ecosystem with strong industry backing, including robust support from major hardware vendors and an open-source community driving continuous innovation. Its toolchain support is extensive, featuring mature GCC and LLVM compilers, comprehensive debugging tools, and growing availability of integrated development environments (IDEs). In contrast, MIPS, while having a long-established ecosystem and mature toolchains, faces challenges in growth and modern adoption as industry focus shifts toward open and flexible architectures like RISC-V.

Market Adoption and Commercial Applications

RISC-V has seen rapid growth in market adoption due to its open-source architecture, attracting startups and established companies seeking customization and cost efficiency. MIPS, with a legacy spanning decades, retains a presence in embedded systems and legacy commercial applications but faces declining market share compared to RISC-V. The flexibility and industry support around RISC-V position it as the preferred choice for emerging AI, IoT, and edge computing markets.

Educational Use and Community Support

RISC-V's open-source architecture fosters extensive community support and collaboration, making it highly accessible for educational institutions and students seeking hands-on experience with modern processor design. MIPS, while historically prevalent in academia, has a proprietary nature that limits customization and slows adaptation in educational settings. The growing ecosystem of RISC-V tools, simulators, and learning resources further enhances its appeal as the preferred choice for teaching computer architecture and embedded systems.

Future Prospects and Industry Trends

RISC-V's open-source architecture drives exponential growth in customization and innovation, rapidly gaining adoption across AI, IoT, and edge computing industries. MIPS, while historically significant with strong legacy in embedded systems, faces challenges adapting to modern open standards and evolving workloads. The industry trend favors RISC-V due to its flexibility, vibrant ecosystem, and accelerating support from major semiconductor companies, positioning it as the dominant architecture in future processor designs.

Instruction Set Architecture (ISA)

RISC-V offers a modular, open-source Instruction Set Architecture (ISA) with extensible base and optional standard extensions, while MIPS features a fixed, proprietary ISA with predefined instruction formats and limited extensibility.

Pipeline Stages

RISC-V typically features a 5-stage pipeline (Fetch, Decode, Execute, Memory, Write-back) similar to MIPS, but RISC-V's open standard allows more flexible pipeline customization and extension compared to the fixed MIPS architecture.

Load-Store Architecture

RISC-V's load-store architecture simplifies instruction sets by exclusively using load and store operations for memory access, leading to improved pipeline efficiency and scalability compared to MIPS.

Register File

RISC-V features a modular and extensible 32-register integer register file with a simpler instruction encoding compared to MIPS's fixed 32-register file architecture, enabling more efficient compiler optimizations and scalability for diverse applications.

Instruction Encoding

RISC-V features a simpler, fixed-length 32-bit instruction encoding designed for extensibility and reduced complexity, whereas MIPS uses a fixed 32-bit instruction format with multiple instruction types but less flexibility for extensions.

Superscalar Support

RISC-V offers more flexible and scalable superscalar support through its modular ISA design compared to MIPS, which has more rigid superscalar capabilities limited by its fixed instruction set architecture.

Privileged Modes

RISC-V offers a more flexible and openly extensible privileged mode architecture compared to MIPS, enabling better customization and security features for modern processor designs.

RV32I vs MIPS32

RV32I offers a simplified, open-source 32-bit instruction set with modular extensions and modern pipeline design, while MIPS32 provides a proprietary, mature 32-bit architecture with established ecosystem support but less flexibility for hardware customization.

Open Source Hardware

RISC-V, as a fully open-source instruction set architecture, offers greater flexibility and community-driven innovation compared to the proprietary nature of MIPS, making it a preferred choice for open source hardware development.

Coprocessor Interface

RISC-V features a flexible, extensible coprocessor interface enabling seamless integration of custom accelerators, whereas MIPS uses a fixed coprocessor architecture with limited scalability.

RISC-V vs MIPS Infographic

njnir.com

njnir.com