SPARC and POWER are RISC-based architectures that prioritize high performance and scalability in computing systems. SPARC processors, developed by Sun Microsystems, emphasize simplicity and efficient multiprocessing, making them well-suited for enterprise servers. POWER architecture, created by IBM, offers robust execution capabilities and advanced parallel processing, enabling superior performance in data-intensive applications and high-performance computing environments.

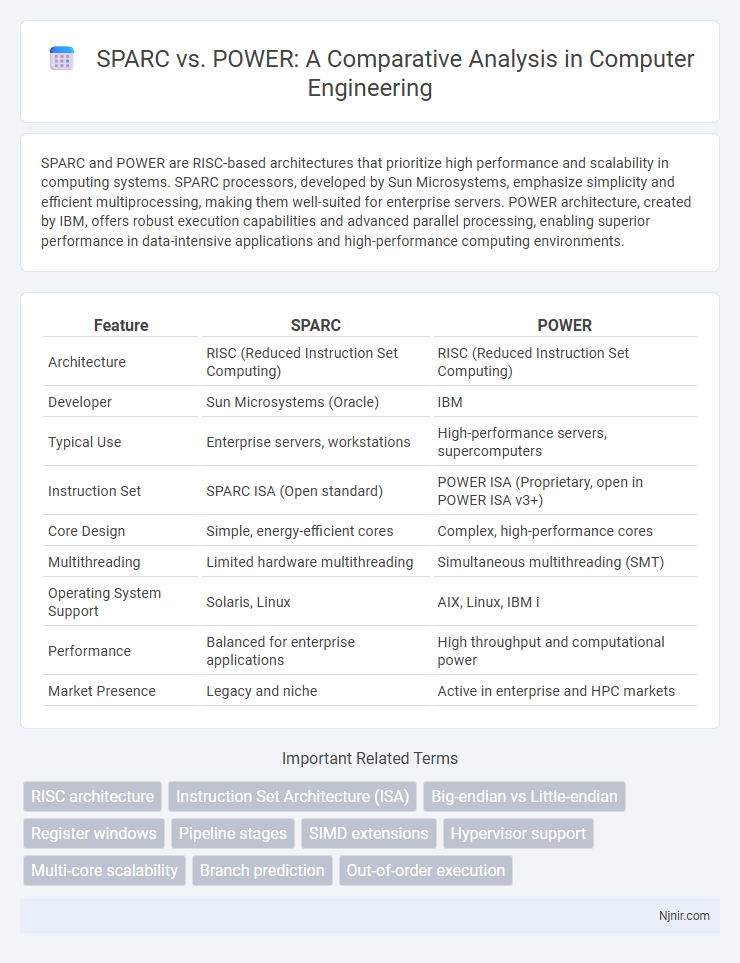

Table of Comparison

| Feature | SPARC | POWER |

|---|---|---|

| Architecture | RISC (Reduced Instruction Set Computing) | RISC (Reduced Instruction Set Computing) |

| Developer | Sun Microsystems (Oracle) | IBM |

| Typical Use | Enterprise servers, workstations | High-performance servers, supercomputers |

| Instruction Set | SPARC ISA (Open standard) | POWER ISA (Proprietary, open in POWER ISA v3+) |

| Core Design | Simple, energy-efficient cores | Complex, high-performance cores |

| Multithreading | Limited hardware multithreading | Simultaneous multithreading (SMT) |

| Operating System Support | Solaris, Linux | AIX, Linux, IBM i |

| Performance | Balanced for enterprise applications | High throughput and computational power |

| Market Presence | Legacy and niche | Active in enterprise and HPC markets |

Introduction to SPARC and POWER Architectures

SPARC (Scalable Processor Architecture) is a RISC (Reduced Instruction Set Computing) design developed by Sun Microsystems, emphasizing scalability and efficient parallel processing in servers and workstations. POWER architecture, created by IBM, features a high-performance RISC design optimized for enterprise-level computing, focusing on advanced instruction execution and multiprocessing capabilities. Both architectures support 64-bit processing and use register windows but differ in design philosophy and target applications within the computing industry.

Historical Development and Evolution

SPARC architecture, developed by Sun Microsystems in the mid-1980s, introduced a RISC-based design that emphasized simplicity and scalability, significantly influencing workstation and server performance during the 1990s. IBM's POWER architecture, launched around the same era, focused on high-performance computing with a sophisticated RISC design that evolved through multiple iterations, powering enterprise servers and supercomputers. Both architectures have continuously advanced, with SPARC integrating multithreading and open standards, while POWER has emphasized parallelism and robust virtualization capabilities, reflecting their distinct evolutionary paths in CPU development.

Core Architectural Differences

SPARC architecture utilizes a RISC design with a focus on high instruction-level parallelism through register windows, enhancing function call efficiency and reducing memory access latency. POWER architecture employs a RISC design as well but emphasizes out-of-order execution and a large number of general-purpose registers to maximize instruction throughput and scalability in multi-threaded workloads. The core difference lies in SPARC's extensive use of register windows for fast context switching versus POWER's sophisticated pipeline and execution units aimed at maximizing raw computational power.

Performance Comparison: SPARC vs POWER

POWER processors consistently deliver superior performance compared to SPARC architectures due to their advanced multicore design and higher clock speeds. POWER CPUs excel in handling large-scale enterprise workloads with efficient parallel processing and greater memory bandwidth, resulting in faster data throughput. SPARC systems, while reliable, often underperform in benchmark tests against POWER, especially in compute-intensive applications and virtualization capabilities.

Instruction Set Architecture (ISA) Analysis

SPARC employs a RISC-based ISA designed for simplicity and high instruction throughput with fixed-length instructions, enabling efficient pipelining and reduced decoding complexity. POWER architecture features a more complex, variable-length ISA supporting both RISC principles and specialized instructions for enhanced performance in computational-intensive tasks, particularly in high-end servers and supercomputers. The fundamental difference lies in SPARC's emphasis on streamlined, predictable instruction execution versus POWER's flexible, performance-oriented instruction set catering to diverse workloads.

Operating System and Software Ecosystem

The SPARC architecture predominantly supports Solaris, known for its robust enterprise features and native support of Oracle's software stack, while also offering compatibility with Linux distributions like Oracle Linux and Debian. POWER architecture excels with IBM's AIX operating system, optimized for high-performance computing and enterprise workloads, and supports a broad range of Linux distributions such as Red Hat Enterprise Linux and SUSE Linux Enterprise Server. The POWER ecosystem is strengthened by open-source software and middleware, including support for containerization via IBM Cloud Paks, whereas SPARC benefits from Oracle's integrated software environment and mission-critical applications.

Scalability and Multithreading Capabilities

SPARC processors excel in scalability through chip multithreading (CMT) technology, allowing hundreds of threads to run concurrently, which enhances throughput in large-scale enterprise environments. POWER processors feature simultaneous multithreading (SMT) with up to eight threads per core, delivering high single-thread performance alongside robust parallelism for demanding workloads. Both architectures prioritize multithreading but differ in execution: SPARC emphasizes massive thread count scalability, while POWER optimizes thread-level parallelism combined with strong per-thread performance.

Energy Efficiency and Power Consumption

SPARC processors are designed with a focus on energy efficiency, utilizing simpler, reduced instruction set computing (RISC) architectures that typically consume less power per operation compared to POWER processors. POWER architectures often deliver higher raw performance but at the cost of increased power consumption and thermal output due to their complex, superscalar designs. Data from SPECpower benchmarks indicates SPARC chips achieve better performance-per-watt ratios in enterprise server environments, making them ideal for energy-conscious data centers.

Use Cases and Industry Applications

SPARC processors excel in enterprise servers and mission-critical applications within financial services, telecommunications, and government sectors due to their high throughput and reliability. POWER architecture finds extensive use in high-performance computing, artificial intelligence, and data analytics, serving industries like aerospace, automotive design, and cloud service providers. Both architectures support virtualization and scalable workloads but diverge as SPARC emphasizes traditional server reliability while POWER targets cutting-edge computational performance.

Future Trends and Roadmap

IBM POWER processors continue to emphasize enhanced AI workloads, advanced cloud integration, and energy-efficient architectures, with roadmap plans targeting exponential performance scalability and open-source collaboration. Oracle's SPARC roadmap prioritizes increasing security features, tighter integration with Oracle software ecosystems, and optimization for big data analytics, maintaining focus on reducing latency and improving throughput. Emerging trends reveal POWER's growing adaptation for heterogeneous computing environments, whereas SPARC advances in specialized hardware acceleration for database workloads.

RISC architecture

SPARC and POWER both utilize RISC architecture emphasizing simplified instructions for enhanced processing efficiency and performance specialization.

Instruction Set Architecture (ISA)

SPARC features a reduced instruction set computing (RISC) ISA designed for simplicity and high instruction throughput, while POWER employs a complex instruction set computing (CISC) ISA optimized for high-performance computing with intricate instruction capabilities.

Big-endian vs Little-endian

SPARC architecture primarily uses big-endian byte order, while POWER architecture supports both big-endian and little-endian modes, allowing greater flexibility for endian-specific applications.

Register windows

SPARC architecture features register windows that reduce procedure call overhead by providing overlapping sets of registers, while POWER architecture relies on a large register file without register windows, emphasizing register renaming and out-of-order execution for performance.

Pipeline stages

SPARC processors typically feature a 5 to 7-stage pipeline optimizing instruction throughput, whereas IBM POWER processors use a deeper pipeline with up to 20 stages to enhance clock speed and instruction-level parallelism.

SIMD extensions

POWER architecture features robust SIMD extensions through AltiVec and VSX for high-performance vector processing, whereas SPARC's SIMD capabilities are more limited, primarily relying on VIS for multimedia acceleration.

Hypervisor support

POWER processors offer advanced hypervisor support with built-in hardware virtualization features, while SPARC systems rely on software-based hypervisors for virtualization capabilities.

Multi-core scalability

POWER processors demonstrate superior multi-core scalability compared to SPARC architectures due to their advanced cache coherence protocols and optimized memory interconnects.

Branch prediction

POWER processors use advanced dynamic branch prediction algorithms with large branch target buffers to improve instruction pipeline efficiency, whereas SPARC architectures typically rely on simpler static or hybrid branch prediction mechanisms resulting in varying prediction accuracy.

Out-of-order execution

POWER processors feature advanced out-of-order execution to enhance parallelism and performance, while traditional SPARC architectures primarily use in-order execution with limited out-of-order capabilities.

SPARC vs POWER Infographic

njnir.com

njnir.com