Power gating and clock gating are two essential techniques in computer engineering aimed at reducing power consumption in integrated circuits. Power gating cuts off the power supply to idle circuit blocks to eliminate leakage current, while clock gating disables the clock signal to inactive logic blocks to minimize dynamic power. Effective implementation of both methods leads to significant improvements in energy efficiency and extended battery life in modern electronic devices.

Table of Comparison

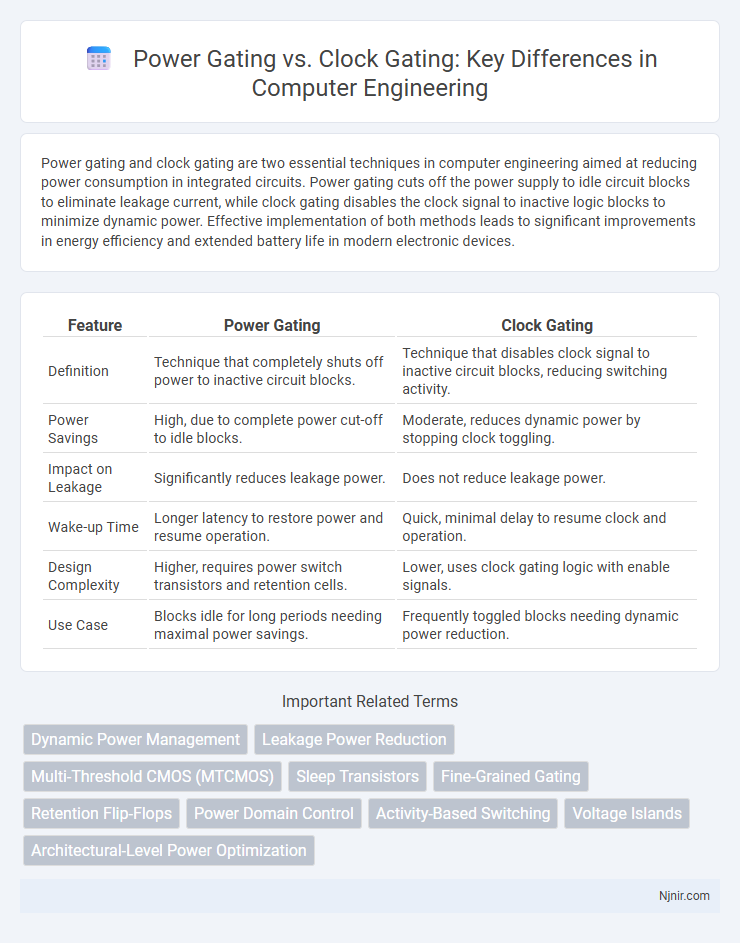

| Feature | Power Gating | Clock Gating |

|---|---|---|

| Definition | Technique that completely shuts off power to inactive circuit blocks. | Technique that disables clock signal to inactive circuit blocks, reducing switching activity. |

| Power Savings | High, due to complete power cut-off to idle blocks. | Moderate, reduces dynamic power by stopping clock toggling. |

| Impact on Leakage | Significantly reduces leakage power. | Does not reduce leakage power. |

| Wake-up Time | Longer latency to restore power and resume operation. | Quick, minimal delay to resume clock and operation. |

| Design Complexity | Higher, requires power switch transistors and retention cells. | Lower, uses clock gating logic with enable signals. |

| Use Case | Blocks idle for long periods needing maximal power savings. | Frequently toggled blocks needing dynamic power reduction. |

Introduction to Power Gating and Clock Gating

Power gating and clock gating are critical techniques in low-power digital circuit design aimed at reducing dynamic and leakage power consumption. Power gating involves physically disconnecting the power supply to idle circuit blocks, effectively minimizing leakage currents during standby mode. Clock gating saves power by disabling the clock signal to inactive sequential elements, preventing unnecessary switching activity and reducing dynamic power usage.

Fundamentals of Power Consumption in Digital Circuits

Power gating and clock gating are critical techniques to reduce dynamic and static power consumption in digital circuits by controlling signal activity and power supply to circuit blocks. Power gating disconnects the power supply to inactive sections, effectively minimizing leakage current, while clock gating disables the clock signal to prevent unnecessary switching, reducing dynamic power caused by capacitive load transitions. Understanding the trade-offs between leakage reduction and performance overhead is essential for optimizing power efficiency in digital integrated circuits.

What is Clock Gating?

Clock gating is a power-saving technique in digital circuits that selectively disables the clock signal to portions of a circuit when they are not in use, reducing dynamic power consumption. By controlling the clock distribution, clock gating minimizes unnecessary switching activity in flip-flops and sequential elements, leading to improved energy efficiency. This method is widely used in microprocessors and ASICs to optimize power without impacting performance during active operation phases.

What is Power Gating?

Power gating is a technique used in integrated circuits to reduce leakage power by shutting off the power supply to inactive blocks or modules, effectively isolating them from the power grid. It involves inserting sleep transistors between the power supply and the circuit sections, enabling complete power shutdown during idle periods and significantly lowering static power consumption. Unlike clock gating, which only stops the clock signal to reduce dynamic power, power gating cuts off power entirely, achieving more substantial energy savings in low-activity states.

Key Differences Between Power Gating and Clock Gating

Power gating reduces leakage power by completely shutting off the power supply to idle circuit blocks, while clock gating saves dynamic power by disabling the clock signal to inactive flip-flops or functional units. Power gating introduces longer wake-up latency due to power domain isolation, whereas clock gating offers faster wake-up times since the circuit remains powered but is temporarily inactive. Implementation complexity is higher in power gating because of the need for power switches and retention strategies, whereas clock gating is simpler to integrate using clock enable signals within the clock distribution network.

Advantages of Clock Gating Techniques

Clock gating significantly reduces dynamic power consumption in digital circuits by disabling the clock signal to inactive modules, preventing unnecessary switching activities. It offers finer control over power savings compared to power gating, which shuts down entire blocks, thus preserving circuit state and enabling faster wake-up times. This technique enhances energy efficiency without the overhead of complex retention strategies required in power gating.

Benefits of Power Gating for Energy Efficiency

Power gating significantly reduces leakage power by completely shutting off the power supply to idle circuit blocks, leading to substantial energy savings in low-activity periods. Unlike clock gating, which only stops the clock signal without cutting off power, power gating minimizes static power consumption, making it ideal for ultra-low-power designs. These benefits contribute to improved battery life and thermal management in mobile and embedded devices, enhancing overall system efficiency.

Common Use Cases and Applications

Power gating is widely used in low-power design for shutting off power to inactive blocks in SoCs and mobile devices, effectively reducing leakage power during idle states. Clock gating is common in microprocessors and digital signal processors to disable clock signals to specific functional units, saving dynamic power without losing data retention. Both techniques are crucial in battery-powered electronics, with power gating targeting long idle periods and clock gating optimizing active workload efficiency.

Design Challenges and Implementation Considerations

Power gating requires careful isolation and retention strategies to prevent data loss and leakage current during power shutdown, posing significant design complexity compared to clock gating. Clock gating, while simpler to implement, demands precise timing control to avoid hazards such as glitches and skew that can compromise circuit reliability. Both techniques must balance power efficiency with performance impact, necessitating advanced synthesis tools and thorough verification to optimize their integration in low-power digital designs.

Future Trends in Power and Clock Gating Techniques

Future trends in power gating and clock gating focus on integrating adaptive power management with machine learning algorithms to optimize energy efficiency at the chip level. Advanced hierarchical gating architectures and ultra-fine-grained gating methods are emerging to reduce leakage currents and dynamic power consumption in next-generation System-on-Chip (SoC) designs. Research also emphasizes combining power gating with multi-threshold voltage technology and dynamic voltage scaling for more intelligent power domains in AI accelerators and IoT devices.

Dynamic Power Management

Power gating significantly reduces dynamic power consumption by completely shutting off power to inactive circuit blocks, whereas clock gating only disables the clock signal to idle modules to minimize switching activity and dynamic power usage.

Leakage Power Reduction

Power gating reduces leakage power by completely shutting off power to idle circuits, while clock gating only minimizes dynamic power by stopping the clock signal without fully eliminating leakage currents.

Multi-Threshold CMOS (MTCMOS)

Power gating using Multi-Threshold CMOS (MTCMOS) effectively reduces leakage power by disconnecting power to idle blocks, while clock gating saves dynamic power by halting clock signals, with MTCMOS enhancing sleep transistor control for improved power savings in power gating.

Sleep Transistors

Sleep transistors in power gating efficiently cut off power to inactive circuit blocks to reduce leakage current, whereas clock gating saves dynamic power by disabling the clock signal without physically disconnecting the power supply.

Fine-Grained Gating

Fine-grained power gating selectively cuts power to inactive circuit blocks to reduce leakage power, while fine-grained clock gating disables the clock signal to idle components to minimize dynamic power consumption.

Retention Flip-Flops

Power gating reduces leakage power by disconnecting the power supply to idle retention flip-flops, while clock gating saves dynamic power by disabling the clock signal, maintaining state retention without interrupting data storage.

Power Domain Control

Power gating controls power supply to entire power domains, significantly reducing leakage power, while clock gating only disables the clock signal within active power domains to minimize dynamic power consumption.

Activity-Based Switching

Power gating reduces leakage power by completely disconnecting power to inactive circuit blocks, while clock gating saves dynamic power by disabling the clock signal to inactive functional units during activity-based switching.

Voltage Islands

Power gating reduces leakage power by completely shutting off voltage islands, while clock gating saves dynamic power by disabling clock signals within active voltage islands.

Architectural-Level Power Optimization

Power gating reduces leakage power by disconnecting power supply to idle blocks, while clock gating minimizes dynamic power by disabling clock signals to inactive modules, both serving as essential architectural-level techniques for energy-efficient integrated circuit design.

Power Gating vs Clock Gating Infographic

njnir.com

njnir.com