High-level synthesis (HLS) transforms abstract algorithmic descriptions into hardware designs, enabling faster development cycles compared to traditional register-transfer level (RTL) design that requires manual coding of hardware behavior. HLS improves productivity by permitting designers to work with higher abstraction languages like C/C++ while automatically generating optimized RTL code for synthesis. Despite HLS's advantages in speed and ease, RTL remains essential for fine-grained control and optimization in complex or highly performance-critical systems.

Table of Comparison

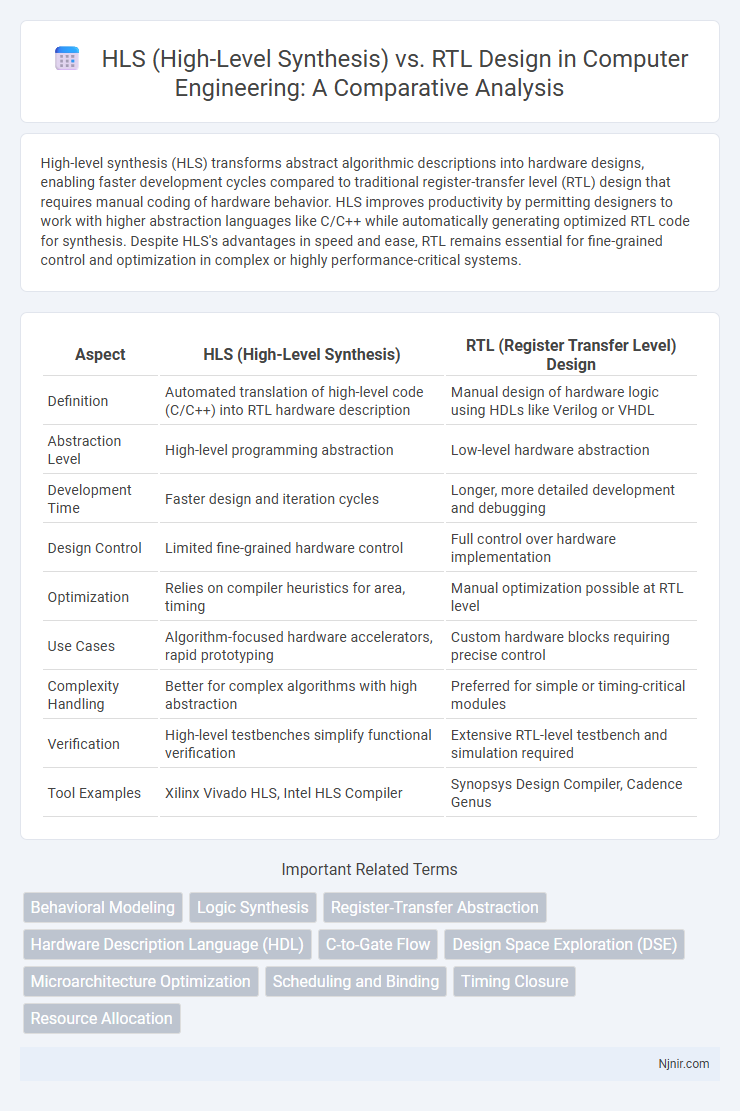

| Aspect | HLS (High-Level Synthesis) | RTL (Register Transfer Level) Design |

|---|---|---|

| Definition | Automated translation of high-level code (C/C++) into RTL hardware description | Manual design of hardware logic using HDLs like Verilog or VHDL |

| Abstraction Level | High-level programming abstraction | Low-level hardware abstraction |

| Development Time | Faster design and iteration cycles | Longer, more detailed development and debugging |

| Design Control | Limited fine-grained hardware control | Full control over hardware implementation |

| Optimization | Relies on compiler heuristics for area, timing | Manual optimization possible at RTL level |

| Use Cases | Algorithm-focused hardware accelerators, rapid prototyping | Custom hardware blocks requiring precise control |

| Complexity Handling | Better for complex algorithms with high abstraction | Preferred for simple or timing-critical modules |

| Verification | High-level testbenches simplify functional verification | Extensive RTL-level testbench and simulation required |

| Tool Examples | Xilinx Vivado HLS, Intel HLS Compiler | Synopsys Design Compiler, Cadence Genus |

Introduction to HLS and RTL Design

High-Level Synthesis (HLS) automates the translation of behavioral code written in C, C++, or SystemC into Register Transfer Level (RTL) descriptions, significantly accelerating the hardware design process. RTL design requires manual coding of hardware algorithms using Hardware Description Languages (HDLs) like VHDL or Verilog, providing fine-grained control over timing and resource allocation. HLS enhances productivity by enabling algorithm-level design and optimization, while RTL offers detailed hardware implementation and precise performance tuning.

Fundamental Concepts: HLS vs RTL

High-level synthesis (HLS) translates high-level programming languages like C/C++ into hardware description languages (HDLs), enabling more abstract, algorithm-driven hardware design compared to Register Transfer Level (RTL), which involves detailed, cycle-accurate descriptions of hardware components and data flow. HLS emphasizes behavioral design abstraction, allowing designers to specify functionality without managing low-level hardware implementation specifics, while RTL demands explicit control of registers, data paths, and timing. This fundamental difference impacts productivity and design exploration, with HLS streamlining complex algorithm mapping and RTL offering precise control over hardware optimization and timing closure.

Design Flow Comparison

High-Level Synthesis (HLS) streamlines the design flow by transforming C/C++ or SystemC code into RTL, significantly reducing development time compared to traditional RTL design, which requires manual writing of hardware description languages like VHDL or Verilog. HLS enables faster exploration of design space and early verification using software simulators, while RTL design offers fine-grained control over hardware implementation and timing optimization. The HLS flow enhances productivity for complex algorithmic designs but may require extensive tuning to meet stringent timing and area constraints achievable with handcrafted RTL.

Abstraction Levels in HLS and RTL

HLS (High-Level Synthesis) operates at a higher abstraction level by allowing designers to describe hardware functionality using high-level programming languages like C/C++, which is then synthesized into RTL code. RTL (Register Transfer Level) design requires manual coding of hardware circuits using hardware description languages such as Verilog or VHDL, focusing on detailed timing, control, and data flow at the register and logic gate level. HLS enhances productivity and design exploration by abstracting complex hardware details, whereas RTL offers precise control over hardware implementation and optimization.

Coding Languages and Toolchains

High-Level Synthesis (HLS) utilizes high-level programming languages such as C, C++, and SystemC to generate hardware designs, enabling faster development cycles and easier algorithmic exploration. In contrast, RTL design relies on hardware description languages (HDLs) like Verilog and VHDL, offering precise control over timing and resource allocation for optimized hardware performance. Toolchains for HLS include platforms like Xilinx Vivado HLS and Cadence Stratus, which automatically convert high-level code to RTL, while RTL design is supported by mature tools such as Synopsys Design Compiler and Mentor Graphics ModelSim for simulation and synthesis.

Productivity and Development Time

High-level synthesis (HLS) significantly improves productivity by enabling designers to describe hardware functionality using high-level languages like C/C++, reducing the coding complexity compared to RTL design, which requires detailed hardware description in languages like Verilog or VHDL. HLS accelerates development time through automated hardware generation and easier modifications, whereas RTL design demands meticulous manual coding and verification, often extending project timelines. The abstraction level in HLS supports faster prototyping and design exploration, leading to shorter time-to-market compared to the labor-intensive RTL design process.

Performance and Optimization Potential

High-level synthesis (HLS) enables automated generation of hardware designs from high-level programming languages, offering rapid design space exploration and improved productivity compared to RTL design. While HLS can achieve performance close to RTL, manual RTL design often provides finer control over timing, resource allocation, and optimization, leading to superior performance in critical applications. Optimization potential in RTL is higher due to precise hardware description, whereas HLS relies on compiler heuristics that may limit aggressive optimizations in complex designs.

Verification and Debugging Approaches

Verification in High-Level Synthesis (HLS) leverages software-like simulations and automated testbenches to quickly identify functional errors at the algorithmic level, while RTL design typically relies on cycle-accurate simulations and waveform analysis to verify hardware-specific timing and behavior. Debugging in HLS benefits from higher abstraction, allowing designers to trace back issues to the original C/C++ source code, whereas RTL debugging requires detailed examination of gate-level signals and low-level timing constraints. Integration of formal verification tools is more mature in RTL workflows, but emerging symbolic execution techniques are increasingly being adapted for HLS to improve coverage and bug detection.

Industry Adoption and Use Cases

High-level synthesis (HLS) accelerates design productivity by enabling automated translation of C/C++ code into register-transfer level (RTL), gaining significant adoption in industries like automotive, aerospace, and AI hardware, where rapid prototyping and verification are crucial. RTL design remains dominant in applications requiring fine-grained hardware control, such as high-frequency trading and custom ASIC development, due to its precision in timing optimization and resource management. Enterprises leverage HLS for complex algorithmic accelerators and early hardware/software co-design, while RTL persists in mission-critical and performance-sensitive projects.

Future Trends in FPGA and ASIC Design

Future trends in FPGA and ASIC design emphasize integrating High-Level Synthesis (HLS) to accelerate development cycles and enhance design productivity by abstracting hardware complexity. HLS enables designers to work at higher abstraction levels, leveraging C/C++ or OpenCL, which supports rapid prototyping and verification compared to traditional Register-Transfer Level (RTL) design. Emerging AI-driven optimization tools combined with HLS workflows are poised to improve power efficiency, area utilization, and performance in next-generation semiconductor architectures.

Behavioral Modeling

High-level synthesis (HLS) enables behavioral modeling through abstract algorithmic descriptions in C/C++ or SystemC, while RTL design requires detailed cycle-accurate hardware description using languages like Verilog or VHDL.

Logic Synthesis

High-level synthesis (HLS) automates logic synthesis by converting C/C++ code into RTL, enabling faster design iterations and higher abstraction, whereas traditional RTL design requires manual coding and optimization at the register-transfer level for precise control over hardware implementation.

Register-Transfer Abstraction

HLS (High-Level Synthesis) automates Register-Transfer Level (RTL) design by converting high-level programming languages into RTL code, enabling faster development and improved abstraction compared to manual RTL coding.

Hardware Description Language (HDL)

High-level synthesis (HLS) compiles algorithms written in high-level languages like C/C++ into Hardware Description Language (HDL) code, automating RTL design and accelerating hardware development compared to traditional manual RTL coding in VHDL or Verilog.

C-to-Gate Flow

C-to-Gate flow in HLS automates the translation of C/C++ code into optimized gate-level RTL, significantly accelerating design cycles compared to manual RTL design while enabling early functional verification and design-space exploration.

Design Space Exploration (DSE)

High-level synthesis (HLS) accelerates Design Space Exploration (DSE) by automating the mapping of high-level algorithmic descriptions to RTL, enabling rapid evaluation of architectural and microarchitectural trade-offs compared to manual RTL design.

Microarchitecture Optimization

HLS enables faster microarchitecture optimization by automating design space exploration and pipelining, while RTL design offers granular control for fine-tuning timing and resource allocation.

Scheduling and Binding

HLS improves scheduling efficiency by automatically optimizing operation timing and resource allocation, while RTL design requires manual scheduling and binding for precise control over hardware implementation.

Timing Closure

HLS accelerates timing closure by enabling higher-level abstractions and automated optimizations, whereas RTL design requires manual, cycle-accurate tuning for precise timing control.

Resource Allocation

High-level synthesis (HLS) enables more efficient resource allocation by abstracting hardware design into high-level code, allowing automated optimization of parallelism and resource sharing compared to manual, fine-grained control in RTL design.

HLS (High-level synthesis) vs RTL design Infographic

njnir.com

njnir.com