JTAG and SWD are two common debugging interfaces used in computer engineering for programming and testing embedded systems. JTAG offers multi-pin connectivity, allowing access to multiple devices in a chain, making it suitable for complex, multi-chip environments. SWD, a two-pin protocol, provides a simpler and faster alternative ideal for ARM-based microcontrollers, with reduced pin count and lower power consumption.

Table of Comparison

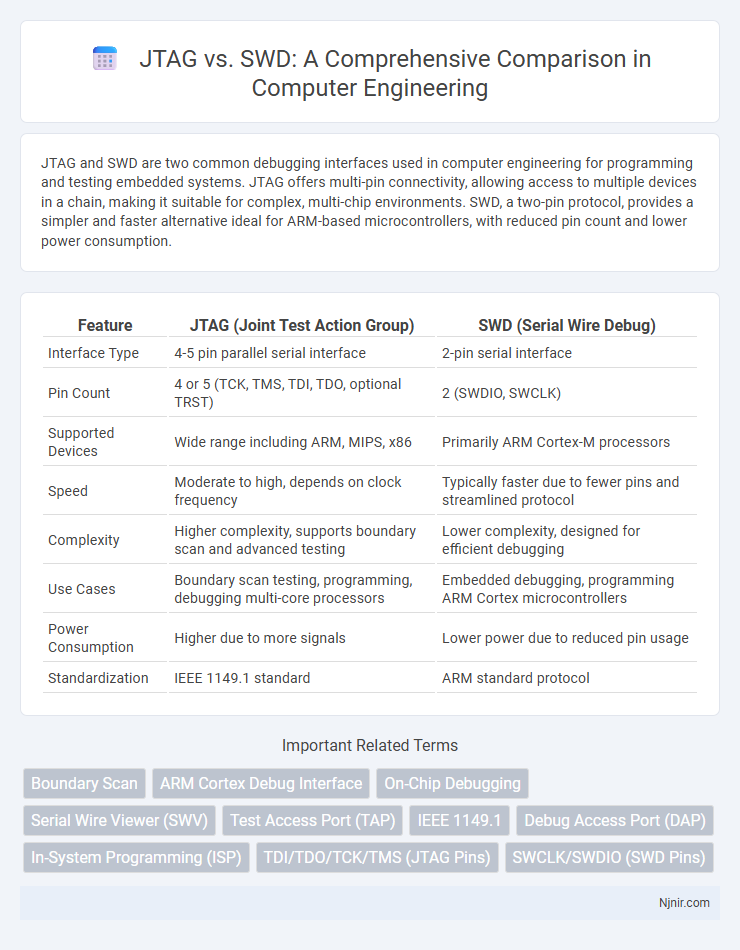

| Feature | JTAG (Joint Test Action Group) | SWD (Serial Wire Debug) |

|---|---|---|

| Interface Type | 4-5 pin parallel serial interface | 2-pin serial interface |

| Pin Count | 4 or 5 (TCK, TMS, TDI, TDO, optional TRST) | 2 (SWDIO, SWCLK) |

| Supported Devices | Wide range including ARM, MIPS, x86 | Primarily ARM Cortex-M processors |

| Speed | Moderate to high, depends on clock frequency | Typically faster due to fewer pins and streamlined protocol |

| Complexity | Higher complexity, supports boundary scan and advanced testing | Lower complexity, designed for efficient debugging |

| Use Cases | Boundary scan testing, programming, debugging multi-core processors | Embedded debugging, programming ARM Cortex microcontrollers |

| Power Consumption | Higher due to more signals | Lower power due to reduced pin usage |

| Standardization | IEEE 1149.1 standard | ARM standard protocol |

Introduction to JTAG and SWD

JTAG (Joint Test Action Group) and SWD (Serial Wire Debug) are standard protocols for debugging and programming embedded systems. JTAG offers a 4 or 5-wire interface allowing access to internal registers and memory, supporting boundary scan testing and multi-core debugging. SWD uses a two-wire interface optimized for ARM Cortex processors, providing a more compact and efficient communication method for debugging and programming.

Overview of Debugging Interfaces in Computer Engineering

JTAG (Joint Test Action Group) and SWD (Serial Wire Debug) are two primary debugging interfaces used in computer engineering to program and debug embedded systems. JTAG offers a standardized 4- or 5-pin interface that supports boundary scan testing and complex multi-core debugging, widely adopted across microcontrollers, FPGAs, and processors. SWD, developed as a streamlined alternative to JTAG by ARM, uses a 2-pin interface optimized for ARM Cortex-M microcontrollers, providing efficient debugging with reduced pin count and lower power consumption.

Understanding JTAG (Joint Test Action Group)

JTAG (Joint Test Action Group) is a standardized interface protocol used for debugging, programming, and testing integrated circuits at the board and chip level. It enables boundary-scan testing, allowing access to internal registers and control logic without physical probes, which is crucial for verifying system functionality and diagnosing faults. JTAG supports multi-device chains, making it suitable for complex boards, whereas SWD (Serial Wire Debug) is a lower-pin alternative primarily designed for ARM Cortex processors offering efficient debugging with fewer signal lines.

Understanding SWD (Serial Wire Debug)

SWD (Serial Wire Debug) is a two-pin interface developed by ARM as a more efficient alternative to the traditional JTAG protocol for debugging ARM Cortex microcontrollers. It uses a single data line (SWDIO) and a clock line (SWCLK) to provide high-speed access to the microcontroller's debug and programming features while minimizing pin usage. SWD delivers equivalent debugging capabilities to JTAG but with reduced complexity and is widely supported in ARM-based development environments.

Key Differences Between JTAG and SWD

JTAG (Joint Test Action Group) and SWD (Serial Wire Debug) are both debugging interfaces used for microcontrollers, with JTAG supporting a 4 to 5-pin interface enabling boundary scan testing and complex debugging tasks. SWD, developed by ARM, uses a simpler 2-pin interface optimized for low pin count and power efficiency, ideal for Cortex-M processors. Key differences include pin count, protocol complexity, and application scope, where JTAG is more versatile for various devices, while SWD is specialized for ARM-based microcontrollers.

Advantages and Disadvantages of JTAG

JTAG offers extensive debugging capabilities and supports multiple devices on a single chain, making it ideal for complex system testing and boundary-scan applications. However, its multi-pin interface can increase hardware complexity and cost compared to the simpler two-pin SWD protocol. JTAG's slower communication speed and increased pin count may limit efficiency and routing flexibility in resource-constrained embedded designs.

Advantages and Disadvantages of SWD

SWD (Serial Wire Debug) offers significant advantages over JTAG by using fewer pins--typically just two--resulting in simpler hardware design and reduced PCB space. Its improved power efficiency and faster debug speeds make it ideal for resource-constrained microcontrollers and embedded systems. However, SWD's narrower data path limits multi-core debugging and trace capabilities compared to JTAG, which can handle complex debugging scenarios more effectively.

Use Cases: When to Choose JTAG or SWD

JTAG is best suited for complex systems requiring boundary-scan testing, multi-core debugging, and programming of large-scale integrated circuits in aerospace or automotive industries. SWD is ideal for low-pin count microcontrollers, such as ARM Cortex-M devices, enabling efficient debugging and programming in embedded and IoT applications. Choose JTAG for advanced diagnostics and multi-device testing, while SWD offers simplicity and speed for resource-constrained environments.

Compatibility and Implementation Considerations

JTAG (Joint Test Action Group) supports a broad range of devices and is widely used for testing and debugging complex integrated circuits, making it highly compatible across various hardware platforms. SWD (Serial Wire Debug), a two-pin interface designed by ARM, offers a more streamlined implementation for ARM Cortex microcontrollers, reducing pin count and simplifying PCB design. Although JTAG provides extensive debugging features, SWD's simplified wiring and lower hardware complexity enhance compatibility in resource-constrained embedded systems.

Conclusion: Selecting the Right Debug Interface

Choosing between JTAG and SWD depends on the target microcontroller's architecture and debugging needs, with JTAG supporting complex multi-core systems and SWD offering a streamlined, low-pin alternative for ARM Cortex-M processors. SWD provides faster programming and lower power consumption, making it ideal for embedded applications requiring minimal hardware overhead. JTAG remains the preferred interface for advanced debugging features and broad device compatibility in high-end or multi-core environments.

Boundary Scan

JTAG supports comprehensive boundary scan testing for detecting interconnect faults on printed circuit boards, while SWD primarily provides a streamlined debug interface with limited boundary scan capabilities.

ARM Cortex Debug Interface

JTAG provides a standard 4- or 5-pin debug interface widely used for ARM Cortex devices, while SWD (Serial Wire Debug) offers a more pin-efficient 2-pin alternative optimized for ARM Cortex debugging.

On-Chip Debugging

JTAG and SWD are On-Chip Debugging protocols where JTAG offers a standardized 4 to 5-pin interface for multi-device boundary scanning, while SWD provides a more efficient 2-pin interface optimized for ARM Cortex microcontrollers.

Serial Wire Viewer (SWV)

Serial Wire Viewer (SWV) in SWD offers real-time data trace and debugging with minimal pin usage compared to JTAG's multi-pin interface, enhancing efficient system monitoring and analysis.

Test Access Port (TAP)

JTAG uses a standardized 4-wire Test Access Port (TAP) for boundary-scan testing and debugging, while SWD employs a simplified 2-wire interface optimized for ARM Cortex processors, enhancing debugging speed and reducing pin count.

IEEE 1149.1

JTAG, defined by the IEEE 1149.1 standard, is a widely adopted boundary-scan architecture enabling device testing and debugging, whereas SWD (Serial Wire Debug) is a more recent ARM-specific debug protocol offering a two-pin interface for efficient access but not governed by IEEE 1149.1.

Debug Access Port (DAP)

The Debug Access Port (DAP) in SWD offers a streamlined two-pin interface for efficient debugging, contrasting with JTAG's multi-pin complexity and broader device support.

In-System Programming (ISP)

JTAG and SWD are both In-System Programming (ISP) protocols, with SWD offering a streamlined, two-pin interface ideal for ARM Cortex-M microcontrollers, while JTAG provides a more complex, multi-pin solution supporting broader device compatibility and advanced debugging features.

TDI/TDO/TCK/TMS (JTAG Pins)

JTAG interfaces use four primary pins--TDI (Test Data In), TDO (Test Data Out), TCK (Test Clock), and TMS (Test Mode Select)--to facilitate serial communication and control of test access ports, while SWD reduces pin count by using only two lines, SWDIO and SWCLK, for efficient debugging.

SWCLK/SWDIO (SWD Pins)

SWCLK and SWDIO pins in SWD provide a two-wire interface for efficient debugging and programming, contrasting with JTAG's multiple-pin protocol for complex test access.

JTAG vs SWD Infographic

njnir.com

njnir.com