VHDL offers strong typing and a more verbose syntax, making it ideal for complex FPGA and ASIC design verification, while Verilog provides a simpler, C-like syntax favored for rapid prototyping and hardware description. VHDL's extensive support for abstraction and concurrency enhances design reliability, whereas Verilog's widespread industry adoption and simulation speed improve developer productivity. Both languages serve unique engineering needs, with VHDL excelling in rigorous, safety-critical designs and Verilog optimizing efficient synthesis and integration.

Table of Comparison

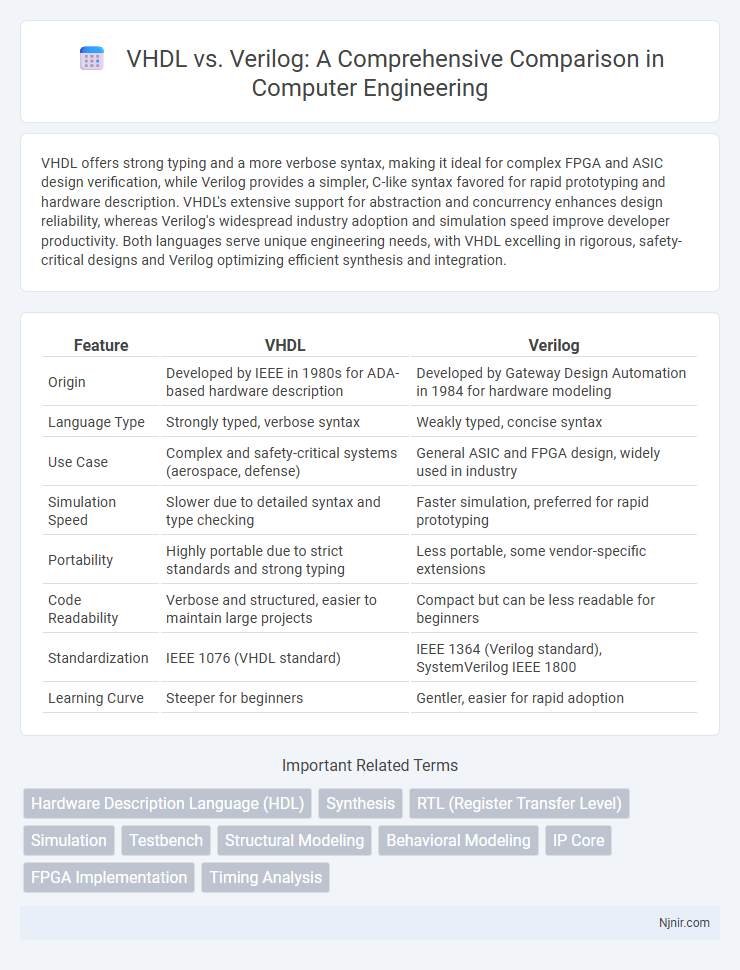

| Feature | VHDL | Verilog |

|---|---|---|

| Origin | Developed by IEEE in 1980s for ADA-based hardware description | Developed by Gateway Design Automation in 1984 for hardware modeling |

| Language Type | Strongly typed, verbose syntax | Weakly typed, concise syntax |

| Use Case | Complex and safety-critical systems (aerospace, defense) | General ASIC and FPGA design, widely used in industry |

| Simulation Speed | Slower due to detailed syntax and type checking | Faster simulation, preferred for rapid prototyping |

| Portability | Highly portable due to strict standards and strong typing | Less portable, some vendor-specific extensions |

| Code Readability | Verbose and structured, easier to maintain large projects | Compact but can be less readable for beginners |

| Standardization | IEEE 1076 (VHDL standard) | IEEE 1364 (Verilog standard), SystemVerilog IEEE 1800 |

| Learning Curve | Steeper for beginners | Gentler, easier for rapid adoption |

Overview of VHDL and Verilog

VHDL (VHSIC Hardware Description Language) and Verilog are both hardware description languages used for designing and modeling electronic systems, particularly FPGAs and ASICs. VHDL is strongly typed and verbose, offering extensive support for complex data types and strong compile-time checking, making it suitable for large-scale, high-reliability projects. Verilog is less strict, with a syntax resembling the C programming language, which often results in faster coding and simulation cycles, favored for rapid prototyping and industry-standard RTL design.

Historical Background and Development

VHDL originated in the early 1980s under the Department of Defense to standardize documentation for ASIC designs, emphasizing strong typing and hardware description precision. Verilog was developed by Gateway Design Automation in 1984 as a simpler, C-like language to accelerate digital design simulation and synthesis. Both languages evolved through standardization processes with IEEE, VHDL as IEEE 1076 and Verilog as IEEE 1364, solidifying their roles in electronic design automation.

Syntax and Language Structure Comparison

VHDL features a strongly typed, verbose syntax emphasizing modularity with distinct entities and architectures, supporting detailed design hierarchy and rigorous type checking. Verilog employs a more concise, C-like syntax with simpler language constructs, facilitating faster coding but offering less strict type enforcement and modular separation. Both languages support concurrent hardware description but differ significantly in language structure, impacting readability, maintainability, and design complexity management.

Simulation and Synthesis Capabilities

VHDL offers strong simulation capabilities with precise timing and type checking, making it suitable for complex designs requiring rigorous verification. Verilog excels in fast synthesis due to its concise syntax and wide industry support, enabling efficient hardware description and implementation. Both languages support comprehensive synthesis tools, but VHDL's strict syntax enhances error detection while Verilog's simulation speed accelerates iterative development.

Toolchain and EDA Support

VHDL offers robust toolchain support from leading EDA vendors such as Mentor Graphics, Synopsys, and Cadence, ensuring advanced simulation, synthesis, and formal verification capabilities. Verilog benefits from widespread integration across popular EDA tools including ModelSim, Vivado, and Quartus, facilitating seamless RTL design and debugging. Both languages are well-supported in contemporary toolchains, but Verilog often has an edge in FPGA-centric workflows, while VHDL excels in aerospace and defense applications with stringent verification requirements.

Popular Use Cases in Industry

VHDL is widely used in aerospace, defense, and automotive industries for designing highly reliable, safety-critical systems due to its strong typing and readability features. Verilog dominates the semiconductor and consumer electronics sectors, favored for rapid prototyping and designing complex digital circuits like CPUs and GPUs, thanks to its concise syntax and vast support in commercial EDA tools. Both languages are essential for FPGA development, with VHDL preferred for stringent hardware validation and Verilog for faster iterative design processes.

Learning Curve and User Community

VHDL features a steeper learning curve due to its strong typing and verbose syntax, which appeals to engineers favoring strict design discipline and documentation. Verilog offers a simpler and more concise syntax, making it easier for beginners and those familiar with C-like languages to adopt quickly. The Verilog user community is larger, supported by extensive open-source projects and industry adoption, while VHDL has a dedicated but smaller community, often favored in aerospace and defense sectors.

Portability and Compatibility

VHDL offers higher portability due to its strict typing and strong syntax rules, making designs more hardware-agnostic and easier to reuse across different platforms. Verilog excels in compatibility, widely supported by most EDA tools and preferred for ASIC development, ensuring smoother integration with existing workflows. Both languages support synthesis and simulation, but VHDL's rigorous standards enhance cross-vendor interoperability while Verilog's extensive library support facilitates compatibility in mixed environments.

Performance and Resource Utilization

VHDL and Verilog differ in performance and resource utilization based on their synthesis and optimization capabilities. Verilog often enables faster simulation and synthesis times due to its simpler syntax and widespread industry support, resulting in efficient resource mapping for FPGA and ASIC designs. VHDL provides strong type checking and abstraction, which can lead to more reliable designs but may require more resources and longer synthesis time depending on the complexity of the hardware description.

Future Trends and Market Adoption

VHDL and Verilog continue to dominate hardware description languages in FPGA and ASIC design, with Verilog gaining more traction in emerging fields like AI hardware and high-speed communication systems due to its concise syntax and extensive tool support. Future trends indicate increased integration of SystemVerilog, which extends Verilog capabilities, and growing adoption of VHDL in safety-critical industries like aerospace, driven by its strong typing and reliability features. Market adoption favors Verilog in commercial semiconductor design, while VHDL remains preferred in defense and aerospace sectors, reflecting distinct ecosystem preferences and evolving industry requirements.

Hardware Description Language (HDL)

VHDL and Verilog are two primary Hardware Description Languages (HDLs) used for designing and simulating digital circuits, with VHDL offering strong typing and verbose syntax ideal for complex designs, while Verilog provides a simpler, C-like syntax preferred for rapid prototyping and synthesis.

Synthesis

VHDL offers strong typing and modular design benefits for synthesis, while Verilog provides simpler syntax and widespread industry support, making both essential for efficient hardware description language synthesis.

RTL (Register Transfer Level)

VHDL offers strong typing and strict syntax for precise RTL design, while Verilog provides a concise, C-like syntax favored for faster RTL coding and easier hardware simulation.

Simulation

VHDL offers strong typing and extensive simulation libraries for accurate hardware modeling, while Verilog provides faster simulation speeds with simpler syntax, making both essential for different simulation needs in digital design.

Testbench

VHDL testbenches provide strong type checking and modularity for verifying digital designs, while Verilog testbenches offer simpler syntax and faster simulation capabilities, making each suitable for different verification needs.

Structural Modeling

Structural modeling in VHDL offers clearer hierarchical design description with strong typing and explicit component instantiation compared to Verilog's more flexible but less strict module-based instantiation.

Behavioral Modeling

VHDL offers strong typing and verbose syntax for detailed behavioral modeling, while Verilog provides concise syntax and is widely preferred for rapid hardware description and simulation in behavioral design.

IP Core

VHDL offers strong typing and robust design verification for IP core development, while Verilog provides simpler syntax and widespread industry adoption, making both suitable for creating reusable and modular IP cores depending on project requirements.

FPGA Implementation

VHDL offers strong typing and modular design advantages for complex FPGA implementations, while Verilog provides a simpler syntax and widespread industry adoption, making it preferred for rapid FPGA prototyping and integration.

Timing Analysis

VHDL offers more precise timing analysis through strong typing and explicit timing constraints, while Verilog provides faster simulation with simpler timing models suitable for rapid prototyping.

VHDL vs Verilog Infographic

njnir.com

njnir.com