RISC (Reduced Instruction Set Computer) architecture features a simplified set of instructions that execute rapidly, enhancing performance through efficient pipelining and parallelism. CISC (Complex Instruction Set Computer) architecture includes a broader range of instructions that aim to reduce the number of cycles per instruction but may introduce complexity and slower execution times. The choice between RISC and CISC impacts processor design, power consumption, and application-specific performance in computer engineering.

Table of Comparison

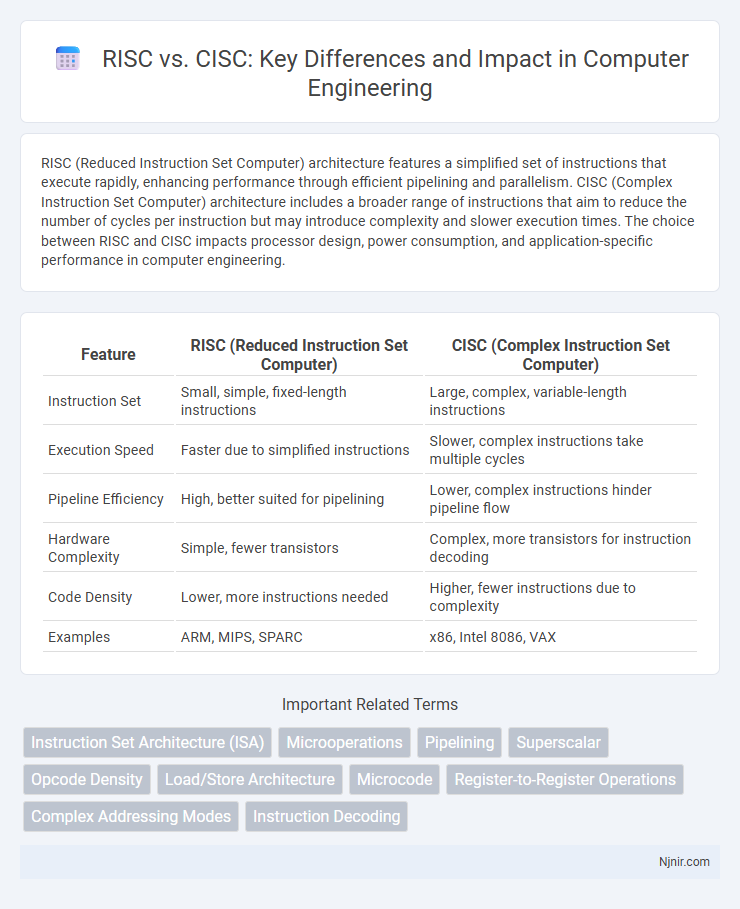

| Feature | RISC (Reduced Instruction Set Computer) | CISC (Complex Instruction Set Computer) |

|---|---|---|

| Instruction Set | Small, simple, fixed-length instructions | Large, complex, variable-length instructions |

| Execution Speed | Faster due to simplified instructions | Slower, complex instructions take multiple cycles |

| Pipeline Efficiency | High, better suited for pipelining | Lower, complex instructions hinder pipeline flow |

| Hardware Complexity | Simple, fewer transistors | Complex, more transistors for instruction decoding |

| Code Density | Lower, more instructions needed | Higher, fewer instructions due to complexity |

| Examples | ARM, MIPS, SPARC | x86, Intel 8086, VAX |

Introduction to RISC and CISC Architectures

RISC (Reduced Instruction Set Computer) architecture simplifies instructions, enabling faster execution and efficient pipelining by using a limited set of simple commands. CISC (Complex Instruction Set Computer) architecture features a wider variety of instructions, designed to execute complex tasks in fewer lines of code, which can reduce memory usage and program size. Both architectures influence processor design, with RISC favoring speed and parallelism, while CISC emphasizes multifunctional instruction capability.

Historical Development of RISC and CISC

The historical development of RISC (Reduced Instruction Set Computer) and CISC (Complex Instruction Set Computer) architectures reflects their differing design philosophies emerging in the 1970s. CISC evolved to execute complex instructions with multiple addressing modes, aiming to reduce the number of instructions per program by increasing instruction complexity, as seen in early Intel x86 processors. RISC, pioneered by research projects at IBM, Stanford, and Berkeley, focused on simplifying instructions to enable faster execution cycles and more efficient pipelining, influencing modern architectures like ARM and MIPS.

Core Principles of RISC Architecture

RISC architecture emphasizes a simplified instruction set that allows for faster instruction execution by using a uniform, fixed instruction length and load/store operations exclusively for memory access. It relies on a large number of general-purpose registers to minimize memory access latency and improve performance through efficient pipelining and parallelism. The core principles of RISC design include reduced instruction complexity, single-cycle instruction execution, and a compiler-friendly instruction set that optimizes instruction throughput.

Key Features of CISC Architecture

CISC architecture is characterized by complex instructions that can execute multiple low-level operations within a single instruction, reducing the number of instructions per program. It features a large set of addressing modes and variable-length instruction formats, enabling sophisticated operations directly in hardware. CISC processors often include microcode for instruction decoding, allowing them to handle tasks like string manipulation and arithmetic more efficiently.

Instruction Set Comparison: RISC vs CISC

RISC (Reduced Instruction Set Computer) features a simplified set of instructions designed for rapid execution, typically completing each instruction in a single clock cycle, while CISC (Complex Instruction Set Computer) includes a larger, more complex set of instructions that can perform multi-step operations within a single instruction. RISC instructions are generally uniform in length and require fewer addressing modes, enhancing pipeline efficiency and reducing decoding complexity, whereas CISC instructions vary in length and support numerous addressing modes, enabling more versatile but slower processing. The streamlined instruction set of RISC facilitates easier implementation of parallelism and optimization in modern processors, contrasting with CISC's legacy focus on minimizing program size through more complex instructions.

Performance Analysis: Speed, Power, and Efficiency

RISC (Reduced Instruction Set Computer) architectures deliver higher performance through simplified instructions that enable faster execution cycles and more efficient pipeline usage, resulting in improved speed compared to CISC (Complex Instruction Set Computer) designs. CISC processors, with their complex instruction sets, often consume more power due to longer decoding stages and variable-length instructions, impacting overall energy efficiency negatively. Performance analysis consistently shows RISC's dominance in power efficiency and speed, especially in mobile and embedded systems, while CISC remains competitive in desktop environments owing to optimized microarchitecture and advanced instruction-level parallelism.

Hardware Complexity and Design Considerations

RISC (Reduced Instruction Set Computer) architecture features simpler hardware design with a smaller set of instructions, enabling faster instruction execution and easier pipeline implementation. CISC (Complex Instruction Set Computer) architecture incorporates more complex instructions, requiring intricate decoding logic and variable instruction lengths, which results in increased hardware complexity and longer design cycles. Design considerations for RISC prioritize efficiency and speed with straightforward control units, while CISC designs focus on maximizing instruction capability at the cost of greater silicon area and power consumption.

Application Domains and Industry Adoption

RISC architectures dominate in mobile devices and embedded systems due to their energy efficiency and simplified instruction sets, making them ideal for smartphones, tablets, and IoT applications. CISC processors, particularly x86, remain prevalent in desktop computing, servers, and high-performance workstations where complex instruction capabilities enhance compatibility and performance for legacy software. The industry trend shows ARM-based RISC designs expanding rapidly in cloud computing and data centers, challenging traditional CISC dominance in enterprise environments.

Compiler and Software Implications

RISC architectures simplify instruction sets, enabling compilers to generate more efficient, streamlined code with consistent instruction execution times and easier pipeline optimization. CISC designs offer complex instructions that can reduce code size but complicate compiler design due to variable instruction lengths and execution timings, challenging optimization and performance tuning. Software targeting RISC benefits from predictable instruction behavior and easier register allocation, while CISC software must address instruction decoding complexity and potential performance unpredictability.

Future Trends in Processor Architecture

Future trends in processor architecture indicate a growing emphasis on RISC (Reduced Instruction Set Computing) designs due to their energy efficiency and scalability for AI and machine learning workloads. Meanwhile, CISC (Complex Instruction Set Computing) architectures continue evolving with enhanced micro-op translation and hybrid approaches to optimize legacy software performance. The convergence of RISC-V open-source processors with CISC features signals a shift toward customizable, high-performance chips tailored for diverse applications in edge computing and cloud environments.

Instruction Set Architecture (ISA)

RISC architectures feature a simplified Instruction Set Architecture with fixed-length instructions and a focus on load/store operations, while CISC architectures utilize complex, variable-length instructions designed to execute multiple low-level operations within a single instruction.

Microoperations

RISC architectures execute simpler microoperations with fewer clock cycles per instruction, while CISC architectures perform more complex microoperations within single instructions, resulting in varied microoperation complexity and execution efficiency.

Pipelining

RISC architectures enable more efficient pipelining with fixed-length instructions and simpler decoding, resulting in higher instruction throughput compared to CISC architectures, which face pipeline hazards due to variable-length instructions and complex decoding processes.

Superscalar

Superscalar architectures in RISC processors enable simultaneous execution of multiple instructions per clock cycle, enhancing performance by exploiting instruction-level parallelism more effectively than traditional CISC designs.

Opcode Density

RISC architectures achieve higher opcode density by utilizing fixed-length, simplified instructions that streamline decoding and increase execution efficiency compared to the variable-length, complex instructions of CISC designs.

Load/Store Architecture

RISC architectures emphasize Load/Store design by restricting memory access to specific instructions, enhancing pipeline efficiency and execution speed compared to CISC's complex memory operations.

Microcode

RISC architectures minimize microcode use by implementing simple, fixed-length instructions executed directly by hardware, while CISC architectures rely heavily on microcode to decode and execute complex, variable-length instructions.

Register-to-Register Operations

RISC architectures prioritize efficient register-to-register operations with a larger number of general-purpose registers and simple instructions, while CISC architectures often rely more on memory-to-register operations with fewer registers and complex instruction sets.

Complex Addressing Modes

RISC processors utilize simple, fixed-length instructions with limited addressing modes to enhance execution speed, while CISC processors support complex addressing modes enabling direct manipulation of memory addresses within instructions for greater flexibility.

Instruction Decoding

RISC processors simplify instruction decoding by using fixed-length, uniform instructions, which enhances decoding speed and efficiency compared to the variable-length, complex instruction decoding required by CISC architectures.

RISC vs CISC Infographic

njnir.com

njnir.com