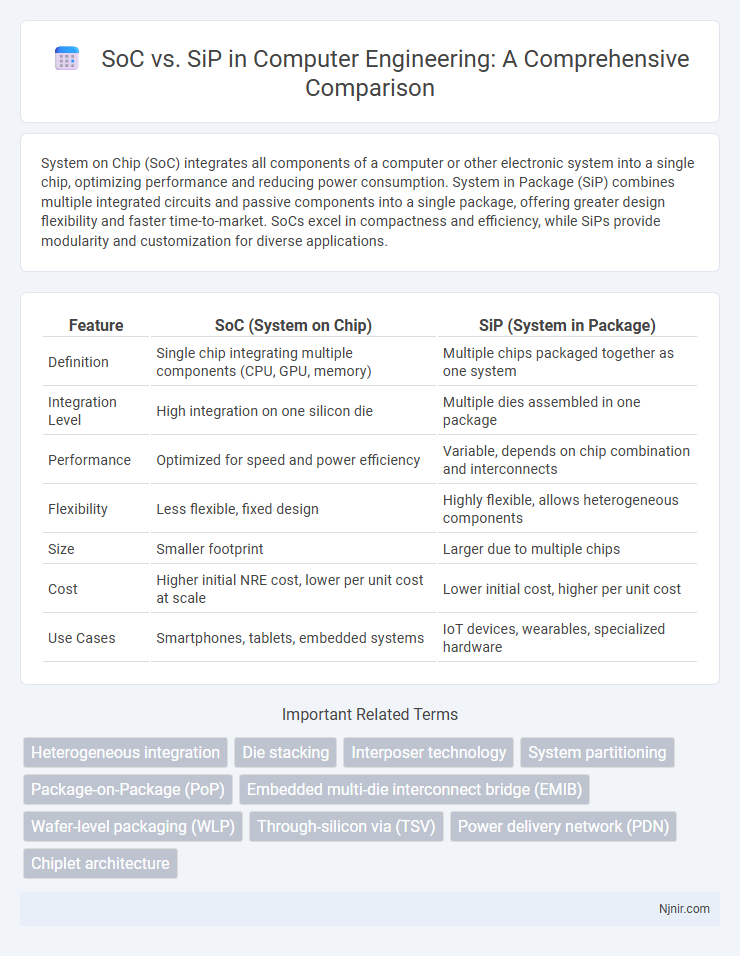

System on Chip (SoC) integrates all components of a computer or other electronic system into a single chip, optimizing performance and reducing power consumption. System in Package (SiP) combines multiple integrated circuits and passive components into a single package, offering greater design flexibility and faster time-to-market. SoCs excel in compactness and efficiency, while SiPs provide modularity and customization for diverse applications.

Table of Comparison

| Feature | SoC (System on Chip) | SiP (System in Package) |

|---|---|---|

| Definition | Single chip integrating multiple components (CPU, GPU, memory) | Multiple chips packaged together as one system |

| Integration Level | High integration on one silicon die | Multiple dies assembled in one package |

| Performance | Optimized for speed and power efficiency | Variable, depends on chip combination and interconnects |

| Flexibility | Less flexible, fixed design | Highly flexible, allows heterogeneous components |

| Size | Smaller footprint | Larger due to multiple chips |

| Cost | Higher initial NRE cost, lower per unit cost at scale | Lower initial cost, higher per unit cost |

| Use Cases | Smartphones, tablets, embedded systems | IoT devices, wearables, specialized hardware |

Introduction to SoC and SiP in Computer Engineering

System on Chip (SoC) integrates all essential electronic circuits of a computer or other system onto a single semiconductor chip, optimizing performance and power efficiency for devices like smartphones and embedded systems. System in Package (SiP) combines multiple integrated circuits and passive components into a single package, enabling heterogeneous integration and improved design flexibility. SoC emphasizes monolithic integration for compactness and speed, while SiP focuses on combining diverse technologies to enhance functionality in constrained spaces.

Defining System on Chip (SoC)

A System on Chip (SoC) integrates multiple electronic components such as the CPU, GPU, memory, and input/output interfaces onto a single semiconductor die, enabling compact, power-efficient, and high-performance computing for devices like smartphones and IoT gadgets. SoCs are designed to optimize system functionality by consolidating various functions into one chip, reducing latency, power consumption, and manufacturing costs. This integration contrasts with Systems in Package (SiP), where multiple separate chips are packaged together but not monolithically integrated at the silicon level.

Understanding System in Package (SiP)

System in Package (SiP) integrates multiple integrated circuits and passive components within a single package, achieving high functionality in a compact form factor. Unlike System on Chip (SoC), which combines components on a single silicon die, SiP offers design flexibility by allowing heterogeneous integration of different technologies and processes. This makes SiP ideal for complex applications requiring miniaturization, such as wearables and IoT devices.

Core Architectural Differences between SoC and SiP

System on Chip (SoC) integrates multiple components such as CPU, GPU, memory, and peripherals into a single silicon die, optimizing power consumption and performance within a compact footprint. System in Package (SiP) combines multiple integrated circuits and passive components into a multi-chip module within one package, allowing heterogeneous technologies to coexist and enabling modular design flexibility. Core architectural differences revolve around SoC's monolithic integration versus SiP's heterogeneous multi-chip assembly, impacting scalability, thermal management, and customization potential.

Integration and Design Complexity

System on Chip (SoC) integrates multiple functions such as CPU, GPU, memory, and peripherals into a single silicon die, resulting in lower power consumption and higher performance efficiency. System in Package (SiP) combines multiple integrated circuits and passive components in a single package, offering design flexibility and shorter time-to-market for complex multi-chip solutions. SoC demands high design complexity due to intricate chip-level integration and advanced manufacturing processes, while SiP simplifies individual chip design but increases package-level integration complexity.

Performance and Power Efficiency Comparison

System on Chip (SoC) integrates all components on a single chip, enabling higher performance through reduced latency and optimized data pathways, which enhances power efficiency by minimizing inter-chip communication. System in Package (SiP) combines multiple specialized chips within one package, offering flexibility but often leading to increased power consumption and lower performance due to inter-chip signaling overhead. SoCs typically outperform SiPs in both speed and energy efficiency because of their monolithic design that streamlines processing and power management.

Cost Implications and Manufacturing Processes

System on Chip (SoC) technology integrates multiple components into a single silicon die, reducing the overall part count and lowering material costs but requiring complex and costly fabrication processes. System in Package (SiP) combines multiple dies in one integrated package, offering modularity and faster time-to-market with potentially higher assembly and testing expenses. SoC manufacturing demands advanced wafer fabrication and design efforts, whereas SiP leverages existing chip technologies with more flexible packaging and interconnection steps, influencing overall cost structures.

Application Scenarios: SoC vs SiP

System on Chip (SoC) is optimized for compact, high-performance devices such as smartphones, tablets, and embedded systems where integration and power efficiency are crucial. System in Package (SiP) excels in applications requiring heterogeneous integration like wearable devices, IoT sensors, and medical implants, offering flexibility by combining multiple chips with diverse functionalities in one package. Both technologies enhance device miniaturization, but SoC suits mass production with uniform function, while SiP supports customization and rapid prototyping in specialized markets.

Future Trends in SoC and SiP Technologies

Future trends in SoC (System on Chip) and SiP (System in Package) technologies emphasize enhanced integration and miniaturization to support advanced AI, 5G, and IoT applications. Increasing adoption of heterogeneous integration and advanced packaging techniques enables higher performance, reduced power consumption, and improved thermal management. Continued innovation in silicon photonics and chiplet architectures drives scalable, high-bandwidth solutions critical for next-generation computing and communication systems.

Choosing the Right Solution: Key Considerations

Choosing between SoC (System on Chip) and SiP (System in Package) depends on factors such as integration complexity, performance requirements, and space constraints. SoC offers higher integration by embedding multiple functions on a single silicon die, ideal for mass production and power efficiency. SiP provides flexibility by combining multiple integrated circuits within a single package, suitable for rapid development and heterogeneous component integration.

Heterogeneous integration

Heterogeneous integration in SoC combines multiple functions on a single chip for optimized performance, while SiP integrates diverse chips and components within a single package to enhance flexibility and system miniaturization.

Die stacking

Die stacking in SoC integrates multiple layers of silicon dies within a single chip to enhance performance and reduce latency, while SiP stacks heterogeneous dies in a compact module to optimize functionality and form factor.

Interposer technology

Interposer technology enhances SiP integration by enabling high-density, high-bandwidth interconnections between heterogeneous components, offering superior flexibility compared to the monolithic design of SoCs.

System partitioning

System partitioning in SoC integrates multiple functions into a single silicon chip, while SiP packages several integrated circuits and passive components within a single module to optimize performance and design flexibility.

Package-on-Package (PoP)

Package-on-Package (PoP) technology stacks separate System on Chip (SoC) and memory components vertically within a Single in Package (SiP) design, optimizing space and improving electrical performance compared to traditional discrete SoC and SiP implementations.

Embedded multi-die interconnect bridge (EMIB)

Embedded Multi-die Interconnect Bridge (EMIB) enhances System on Chip (SoC) and System in Package (SiP) designs by enabling high-density, high-bandwidth interconnects between multiple dies within a compact package, significantly improving performance and power efficiency.

Wafer-level packaging (WLP)

Wafer-level packaging (WLP) enhances SiP integration by enabling compact, high-performance assemblies compared to traditional SoC packaging methods.

Through-silicon via (TSV)

Through-silicon via (TSV) technology enhances SoC integration by enabling vertical electrical connections within a single chip, while SiP leverages TSV to stack multiple chips vertically, improving inter-chip communication and overall device miniaturization.

Power delivery network (PDN)

System on Chip (SoC) integrates a centralized Power Delivery Network (PDN) enhancing power efficiency and minimizing voltage drop compared to System in Package (SiP), where multiple dies require complex PDN management for stable power distribution.

Chiplet architecture

Chiplet architecture enhances SoC and SiP designs by modularizing integrated circuits into smaller, reusable chiplets, optimizing performance, scalability, and manufacturing flexibility.

SoC vs SiP Infographic

njnir.com

njnir.com