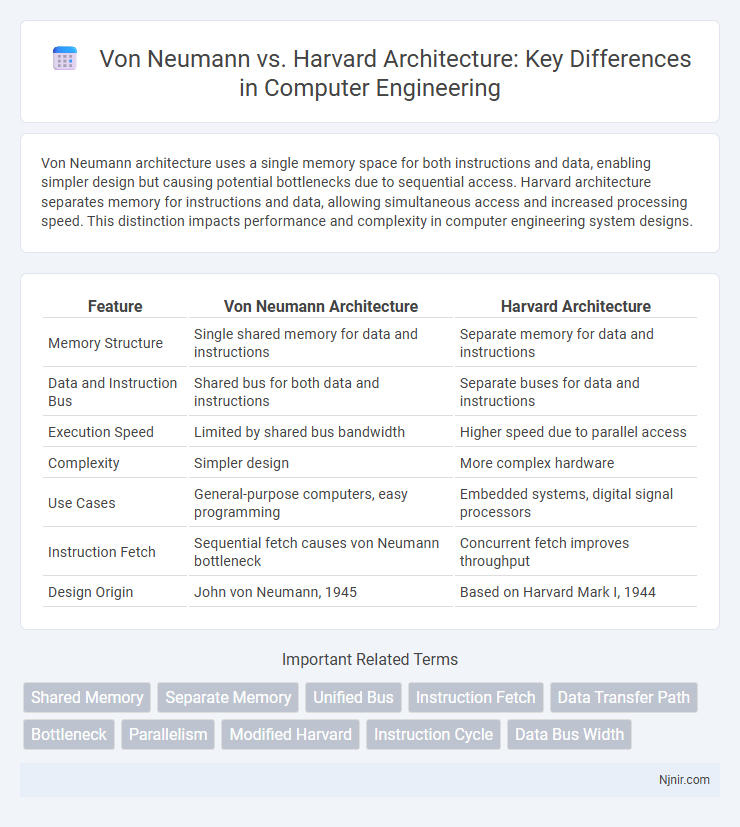

Von Neumann architecture uses a single memory space for both instructions and data, enabling simpler design but causing potential bottlenecks due to sequential access. Harvard architecture separates memory for instructions and data, allowing simultaneous access and increased processing speed. This distinction impacts performance and complexity in computer engineering system designs.

Table of Comparison

| Feature | Von Neumann Architecture | Harvard Architecture |

|---|---|---|

| Memory Structure | Single shared memory for data and instructions | Separate memory for data and instructions |

| Data and Instruction Bus | Shared bus for both data and instructions | Separate buses for data and instructions |

| Execution Speed | Limited by shared bus bandwidth | Higher speed due to parallel access |

| Complexity | Simpler design | More complex hardware |

| Use Cases | General-purpose computers, easy programming | Embedded systems, digital signal processors |

| Instruction Fetch | Sequential fetch causes von Neumann bottleneck | Concurrent fetch improves throughput |

| Design Origin | John von Neumann, 1945 | Based on Harvard Mark I, 1944 |

Overview of Computer Architectures

Von Neumann architecture features a single memory space for both instructions and data, enabling simpler design but causing potential bottlenecks due to shared bus usage. Harvard architecture separates memory storage and pathways for instructions and data, allowing simultaneous access and improving speed in embedded and DSP systems. Modern processors often incorporate a modified Harvard architecture to optimize performance while maintaining flexibility.

Key Principles of Von Neumann Architecture

Von Neumann architecture is characterized by a single memory space that stores both instructions and data, enabling the CPU to access them using the same bus system. This unified memory structure simplifies design but can lead to the "Von Neumann bottleneck," where instruction fetch and data operation cannot occur simultaneously. The architecture employs a sequential instruction processing model, relying on a program counter to track the execution sequence.

Key Principles of Harvard Architecture

Harvard architecture features separate memory spaces for instructions and data, allowing simultaneous access that enhances processing speed and efficiency. It uses distinct buses for instruction and data transfers, reducing bottlenecks common in shared memory designs. This separation optimizes pipeline performance in modern CPUs and is prevalent in microcontrollers and DSPs for real-time applications.

Memory Organization Differences

Von Neumann architecture uses a single shared memory space for both instructions and data, which can lead to bottlenecks as the CPU must access them sequentially. Harvard architecture employs separate memory units for instructions and data, enabling simultaneous access and improving processing speed. This separation in Harvard architecture enhances performance by allowing parallel instruction and data fetches, reducing latency compared to the unified approach of Von Neumann.

Instruction and Data Pathways

Von Neumann architecture utilizes a single memory system for both instructions and data, causing a bottleneck known as the Von Neumann bottleneck due to shared pathways. Harvard architecture separates instruction and data memory, allowing simultaneous access and increasing throughput by eliminating contention between instruction fetch and data operations. This separation in Harvard architecture leads to faster processing speeds and improved efficiency in pipelined CPU designs.

Performance and Bottleneck Issues

The Von Neumann architecture faces a significant bottleneck due to its single memory pathway for both instructions and data, which limits performance through slower data access speeds. In contrast, the Harvard architecture separates memory storage and pathways for instructions and data, allowing simultaneous access that enhances throughput and reduces latency. Consequently, Harvard architecture typically outperforms Von Neumann designs in applications requiring high-speed processing and efficient data handling.

Application Areas and Use Cases

Von Neumann architecture is predominantly used in general-purpose computing systems such as desktops, laptops, and servers, where flexibility and ease of programming are essential. Harvard architecture is favored in embedded systems, digital signal processors (DSPs), and microcontrollers, offering higher performance in time-critical applications due to its separate memory pathways for instructions and data. The distinction in memory design enables Harvard architecture to excel in specialized fields like real-time processing and signal processing, while Von Neumann remains suited for versatile, multi-functional computing tasks.

Security and Isolation Considerations

Harvard architecture inherently enhances security and isolation by separating instruction and data memory, preventing unauthorized code execution and data corruption attacks. Von Neumann architecture, with its unified memory for instructions and data, is more vulnerable to exploits such as buffer overflows and code injection because instructions can be inadvertently overwritten or manipulated. Implementing hardware-based memory protection units in Von Neumann systems is critical to mitigate isolation risks and strengthen overall system security.

Power Efficiency and Hardware Complexity

Von Neumann architecture typically consumes more power due to the unified memory system causing bottlenecks and frequent access conflicts, increasing energy consumption. Harvard architecture separates instruction and data memory, reducing access time and improving power efficiency by enabling simultaneous data fetches. However, this separation increases hardware complexity and cost due to duplicated memory buses and control logic.

Modern Implementations and Hybrid Approaches

Modern implementations of Von Neumann architecture leverage unified memory systems to simplify design and reduce costs in general-purpose CPUs, while Harvard architecture is predominantly used in microcontrollers and digital signal processors for enhanced performance through separate instruction and data pathways. Hybrid approaches combine elements of both architectures by utilizing a unified main memory with distinct caches for instructions and data, optimizing speed and efficiency in contemporary processors. These hybrid designs are prominent in modern CPU cores, balancing throughput and complexity in applications ranging from mobile computing to high-performance servers.

Shared Memory

Von Neumann architecture uses a single shared memory for both instructions and data, while Harvard architecture employs separate memory spaces for instructions and data to enable simultaneous access.

Separate Memory

Harvard architecture uses separate memory modules for instructions and data, enabling simultaneous access and faster processing compared to Von Neumann architecture's shared memory.

Unified Bus

Von Neumann architecture uses a single unified bus for both data and instructions, leading to potential bottlenecks, whereas Harvard architecture employs separate buses, allowing simultaneous access and improved performance.

Instruction Fetch

Von Neumann architecture uses a single memory space for instructions and data, causing instruction fetch to compete with data access, while Harvard architecture has separate memory for instructions and data, enabling simultaneous instruction fetch and data access for faster processing.

Data Transfer Path

Von Neumann architecture uses a single data transfer path for instructions and data between memory and the CPU, whereas Harvard architecture employs separate data transfer paths, enabling simultaneous instruction and data access for improved performance.

Bottleneck

The Von Neumann architecture suffers from a bottleneck due to its single shared memory for instructions and data, limiting throughput compared to the Harvard architecture's separate memory pathways.

Parallelism

Harvard architecture enables higher parallelism through separate memory pathways for instructions and data, while Von Neumann architecture's single memory bus limits simultaneous access and reduces parallel processing efficiency.

Modified Harvard

Modified Harvard architecture improves performance by separating instruction and data caches while allowing shared memory access, combining advantages of Von Neumann and Harvard designs.

Instruction Cycle

The Von Neumann architecture executes its instruction cycle by sequentially fetching instructions and data from a shared memory using a single bus, whereas the Harvard architecture performs parallel instruction and data fetches through separate memory and buses, significantly improving processing speed and efficiency.

Data Bus Width

Von Neumann architecture uses a single, narrower data bus for both instructions and data, while Harvard architecture employs separate, wider data buses to enable simultaneous instruction and data access, enhancing throughput.

Von Neumann vs Harvard architecture Infographic

njnir.com

njnir.com