UVM (Universal Verification Methodology) enhances SystemVerilog by providing a standardized framework for designing reusable and scalable verification environments. While SystemVerilog offers powerful language constructs for hardware description and verification, UVM builds on these features to enable advanced testbench architecture, transaction-level modeling, and automated test generation. The integration of UVM with SystemVerilog significantly improves verification efficiency and debugging capabilities for complex computer engineering designs.

Table of Comparison

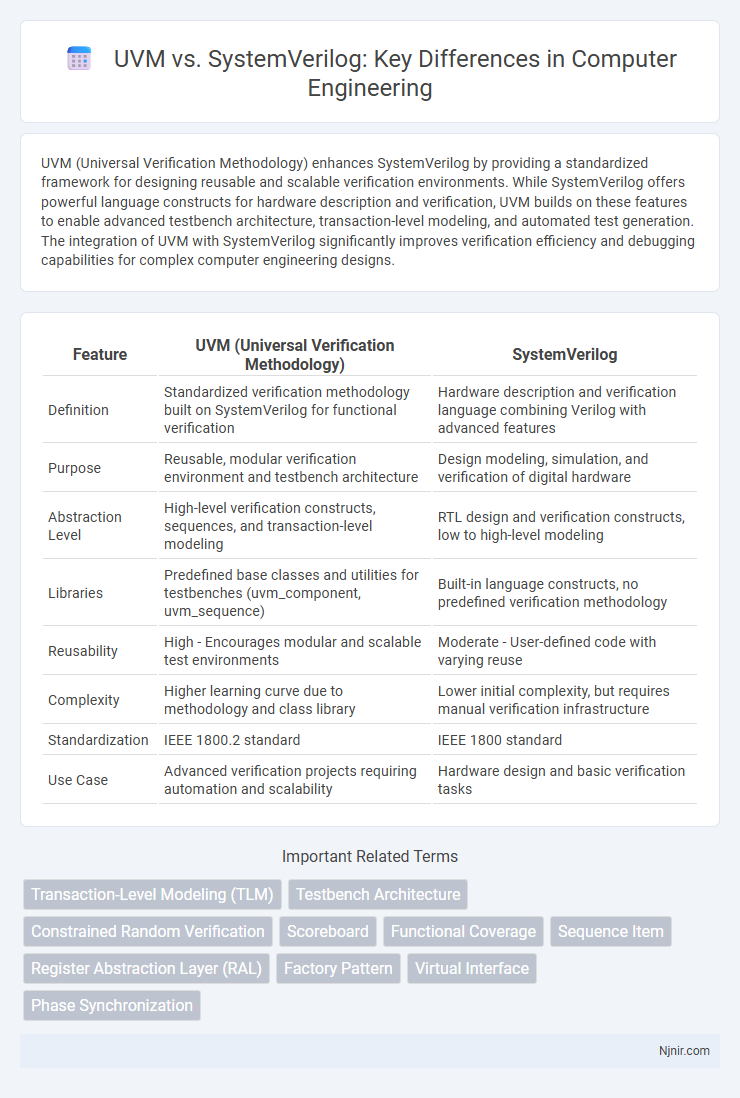

| Feature | UVM (Universal Verification Methodology) | SystemVerilog |

|---|---|---|

| Definition | Standardized verification methodology built on SystemVerilog for functional verification | Hardware description and verification language combining Verilog with advanced features |

| Purpose | Reusable, modular verification environment and testbench architecture | Design modeling, simulation, and verification of digital hardware |

| Abstraction Level | High-level verification constructs, sequences, and transaction-level modeling | RTL design and verification constructs, low to high-level modeling |

| Libraries | Predefined base classes and utilities for testbenches (uvm_component, uvm_sequence) | Built-in language constructs, no predefined verification methodology |

| Reusability | High - Encourages modular and scalable test environments | Moderate - User-defined code with varying reuse |

| Complexity | Higher learning curve due to methodology and class library | Lower initial complexity, but requires manual verification infrastructure |

| Standardization | IEEE 1800.2 standard | IEEE 1800 standard |

| Use Case | Advanced verification projects requiring automation and scalability | Hardware design and basic verification tasks |

Introduction to UVM and SystemVerilog

SystemVerilog is a comprehensive hardware description and verification language that extends Verilog with advanced features for design and testbench development, including object-oriented programming and assertions. UVM (Universal Verification Methodology) builds on SystemVerilog, providing a standardized framework and reusable class libraries for efficient verification of complex integrated circuits. UVM enhances SystemVerilog's capabilities by introducing a structured approach to testbench architecture, stimulus generation, and result analysis, facilitating scalable and maintainable verification environments.

Fundamental Differences Between UVM and SystemVerilog

SystemVerilog is a hardware description and verification language providing constructs for modeling, design, and verification of digital circuits, whereas UVM (Universal Verification Methodology) is a standardized verification methodology built on SystemVerilog for creating reusable, scalable testbenches. SystemVerilog encompasses data types, interfaces, and procedural blocks, while UVM introduces advanced verification components like sequencers, drivers, scoreboards, and a layered testbench architecture to automate and streamline complex verification tasks. The fundamental difference lies in SystemVerilog being a language specification and UVM serving as a methodology leveraging that language to improve verification productivity and quality.

Key Features of SystemVerilog

SystemVerilog enhances traditional Verilog by integrating advanced data types, assertions, and object-oriented programming features essential for modern hardware verification. It supports interfaces and constrained random stimulus generation, enabling more efficient and reusable testbench development. These capabilities, combined with built-in functional coverage and clocking blocks, make SystemVerilog pivotal for complex system-level design and verification.

UVM Architecture Overview

UVM architecture is built on a layered framework that enhances SystemVerilog's capabilities for verification by providing reusable verification components (UVCs) and standardized methodology. Its core components include the sequencer, driver, monitor, and scoreboard, which collectively facilitate stimulus generation, device interaction, result checking, and coverage collection. This modular and scalable design improves testbench organization, promotes code reuse, and supports complex verification tasks in SoC and IP block verification.

Testbench Development: SystemVerilog vs UVM

SystemVerilog offers a flexible, language-level framework for writing testbenches with built-in support for constrained random stimulus, assertions, and coverage, enabling basic to intermediate verification environments. UVM builds on SystemVerilog by providing a comprehensive class library and methodology that standardizes testbench architecture, promoting reusable components, layered verification environments, and scalable test development. While SystemVerilog allows custom testbench designs, UVM accelerates complex verification by facilitating standardized communication between testbench components like drivers, monitors, and scoreboards.

Reusability and Scalability in UVM and SystemVerilog

UVM (Universal Verification Methodology) offers superior reusability through standardized base classes and modular testbench components, enabling efficient test environment replication and extension across projects. SystemVerilog provides foundational language constructs for verification but lacks the structured reuse framework that UVM facilitates, making scalability less streamlined in complex verification environments. By leveraging UVM's factory pattern and configuration database, verification engineers achieve scalable testbench architectures that adapt swiftly to evolving design requirements.

Debugging and Verification Methodologies

UVM (Universal Verification Methodology) enhances SystemVerilog by providing a standardized framework for verification, enabling efficient testbench automation and reuse. Its built-in reporting and phasing mechanisms simplify debugging by offering detailed transaction-level visibility and controlled simulation flow. SystemVerilog alone offers powerful assertions and coverage features, but UVM's layered architecture and standardized components significantly improve verification scalability and debug effectiveness in complex SoC designs.

Integration with Industry Tools

UVM (Universal Verification Methodology) offers robust integration with industry tools such as Synopsys VCS, Cadence Incisive, and Mentor Questa, streamlining testbench development and enhancing simulation efficiency. SystemVerilog, as a language standard, provides foundational features that these tools leverage for code coverage, assertion-based verification, and debugging capabilities. The synergy between UVM and SystemVerilog facilitates seamless interoperability with popular EDA platforms, accelerating the verification cycle and improving productivity in complex chip design environments.

Performance and Productivity Comparison

UVM, built on SystemVerilog, enhances verification productivity by providing reusable testbench components, standardized methodology, and automation features that reduce development time. SystemVerilog alone offers powerful language constructs for hardware description and verification but lacks the structured framework UVM delivers, potentially leading to longer setup and debugging phases. Performance-wise, UVM may introduce slight overhead due to its abstraction layers, yet this is often offset by faster test development and improved verification coverage, resulting in overall productivity gains.

Choosing the Right Approach for Your Project

Selecting between UVM and SystemVerilog depends on project complexity and verification goals, with UVM offering a standardized methodology for scalable and reusable testbenches suited for large projects. SystemVerilog provides fundamental language features ideal for smaller designs or teams requiring a simpler setup without extensive infrastructure. Evaluating team expertise, project size, and verification requirements ensures a choice that maximizes efficiency and accelerates time-to-market.

Transaction-Level Modeling (TLM)

UVM enhances SystemVerilog's Transaction-Level Modeling (TLM) by providing standardized interfaces and communication mechanisms that improve reusable testbench components and efficient data exchange.

Testbench Architecture

UVM offers a standardized, reusable testbench architecture with built-in transaction-level modeling and automation features, while SystemVerilog provides flexible but less structured testbench components requiring manual integration and customization.

Constrained Random Verification

UVM provides a standardized, reusable framework that enhances SystemVerilog's constrained random verification by offering advanced testbench components, improved stimulus generation, and efficient coverage-driven verification capabilities.

Scoreboard

UVM Scoreboard provides a standardized, reusable verification component for automated transaction checking and functional coverage in SystemVerilog testbenches.

Functional Coverage

UVM provides advanced, reusable functional coverage components and automated coverage collection mechanisms, enhancing SystemVerilog's basic functional coverage capabilities for more efficient verification.

Sequence Item

UVM sequence items extend SystemVerilog classes to encapsulate data and stimulus for reusable, modular testbench sequences in advanced verification environments.

Register Abstraction Layer (RAL)

UVM's Register Abstraction Layer (RAL) provides a standardized, reusable model for defining and accessing hardware registers, offering enhanced automation and consistency compared to SystemVerilog's manual register modeling.

Factory Pattern

The UVM Factory Pattern in SystemVerilog enables dynamic object creation and substitution at runtime, enhancing testbench flexibility and reusability compared to traditional static instantiation.

Virtual Interface

UVM leverages SystemVerilog's virtual interface feature to enable modular and reusable testbench components by providing dynamic binding between design and verification environments.

Phase Synchronization

UVM provides built-in phase synchronization mechanisms through its sequencer and driver interaction model, enabling precise control over stimulus timing, whereas SystemVerilog requires explicit coding for phase synchronization within testbench components.

UVM vs SystemVerilog Infographic

njnir.com

njnir.com