Verilog and VHDL are two primary hardware description languages used in computer engineering for designing and modeling digital systems. Verilog offers a syntax similar to the C programming language, making it more approachable for engineers with a software background, while VHDL provides strong typing and strict syntax that enhances design reliability and error checking. Choosing between Verilog and VHDL depends on project requirements, design complexity, and team expertise, as both languages have extensive tool support and are widely adopted in FPGA and ASIC development.

Table of Comparison

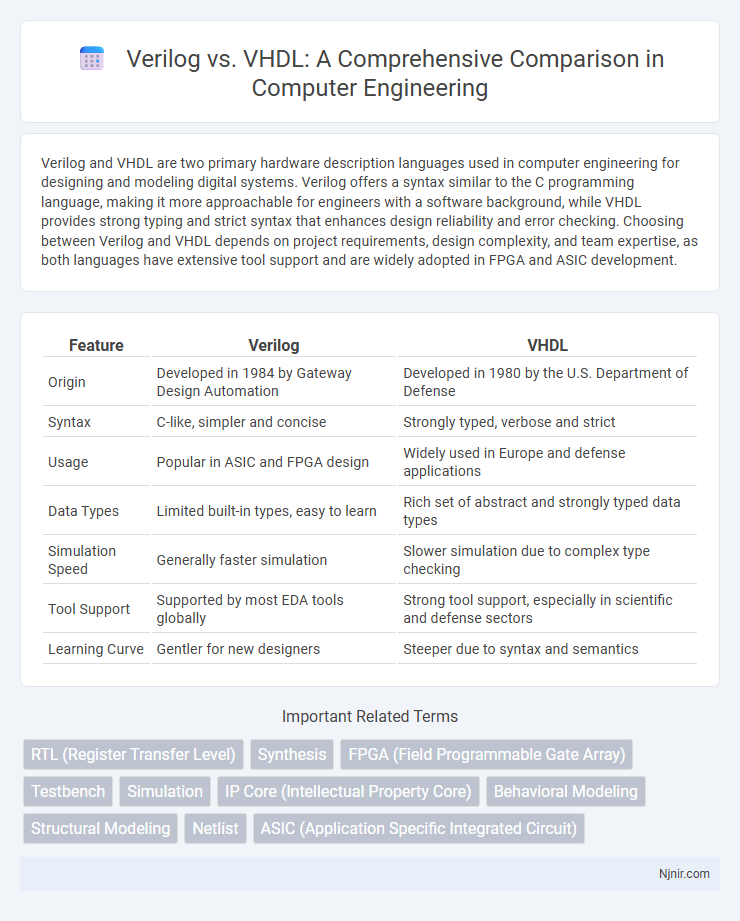

| Feature | Verilog | VHDL |

|---|---|---|

| Origin | Developed in 1984 by Gateway Design Automation | Developed in 1980 by the U.S. Department of Defense |

| Syntax | C-like, simpler and concise | Strongly typed, verbose and strict |

| Usage | Popular in ASIC and FPGA design | Widely used in Europe and defense applications |

| Data Types | Limited built-in types, easy to learn | Rich set of abstract and strongly typed data types |

| Simulation Speed | Generally faster simulation | Slower simulation due to complex type checking |

| Tool Support | Supported by most EDA tools globally | Strong tool support, especially in scientific and defense sectors |

| Learning Curve | Gentler for new designers | Steeper due to syntax and semantics |

Introduction to Verilog and VHDL

Verilog and VHDL are prominent hardware description languages used for digital circuit design and simulation, each offering unique syntax and structural features. Verilog, known for its concise syntax and C-like structure, enables efficient modeling and synthesis of complex hardware systems. VHDL, with its strong typing and verbose syntax, supports detailed and highly descriptive hardware representation, facilitating rigorous verification and portability across diverse FPGA and ASIC platforms.

Historical Evolution of HDL Languages

Verilog and VHDL emerged in the 1980s as foundational hardware description languages, with Verilog developed by Gateway Design Automation in 1984 and standardized as IEEE 1364 in 1995, and VHDL originated from a U.S. Department of Defense initiative in 1981, standardized as IEEE 1076 in 1987. Both languages revolutionized digital design by enabling simulation and synthesis of hardware components, yet their differing syntax and adoption in various industries reflect distinct historical and technical influences. Over time, ongoing standards development and toolchain support have sustained their relevance in FPGA and ASIC design workflows.

Syntax Comparison: Verilog vs VHDL

Verilog syntax is concise and similar to C, making it easier for designers with programming backgrounds to learn, featuring simple keyword usage like "module," "always," and "assign." VHDL syntax is more verbose and strongly typed, emphasizing descriptive code with keywords such as "entity," "architecture," and "process," which helps in designing complex and highly reliable digital circuits. The distinct syntax styles influence code readability and debugging efficiency, where Verilog favors brevity and VHDL prioritizes clarity and strict type enforcement.

Design Abstraction Levels Supported

Verilog supports design abstraction primarily at the behavioral and register-transfer levels (RTL), making it suitable for digital circuit modeling and verification. VHDL extends support across multiple abstraction levels including behavioral, RTL, gate level, and switch level, offering a more comprehensive design approach. The choice between Verilog and VHDL depends on project requirements for abstraction depth, simulation accuracy, and hardware description expressiveness.

Simulation and Synthesis Differences

Verilog offers faster simulation speeds due to its concise syntax and event-driven nature, making it ideal for quick functional verification, while VHDL provides more detailed and strongly-typed constructs that enable precise modeling and error checking during simulation. In synthesis, VHDL's strict type system and modular structure ensure better design reliability and easier debugging in complex FPGA and ASIC designs, whereas Verilog's simpler and more flexible syntax allows faster synthesis turnaround but may require careful coding to avoid synthesis mismatches. Tool support varies, with Verilog favored in digital ASIC design for high-speed synthesis and VHDL preferred in safety-critical applications thanks to its robust simulation semantics and synthesis predictability.

Toolchain and Industry Support

Verilog boasts extensive toolchain compatibility with major EDA tools like Synopsys Design Compiler and Cadence Genus, making it highly favored in the semiconductor industry for ASIC and FPGA design. VHDL offers robust support through tools such as Mentor Graphics ModelSim and Aldec Riviera, excelling in aerospace and defense sectors where stringent verification and reliability standards prevail. Industry adoption trends highlight Verilog in commercial silicon design and VHDL in mission-critical applications, reflecting their optimized integration within respective development ecosystems.

Coding Efficiency and Readability

Verilog offers concise syntax and a C-like structure that often leads to faster coding and easier adoption among programmers familiar with software development, enhancing coding efficiency. VHDL provides strong typing and a more verbose but highly descriptive syntax, which improves readability and reduces errors by enforcing strict design constraints. Choosing between Verilog and VHDL depends on project requirements, where Verilog excels in rapid prototyping and VHDL suits complex designs needing clarity and maintainability.

Error Handling and Debugging Features

Verilog provides limited built-in error handling mechanisms, primarily relying on simulation tools for debugging and waveform analysis, which can make tracking complex design issues challenging. VHDL offers more robust error detection capabilities through strong typing, explicit signal declarations, and assertion statements that enable early identification of mismatches and logical errors during simulation. The advanced assertion-based verification and comprehensive reporting features in VHDL facilitate more efficient debugging and higher design reliability compared to Verilog.

Application Areas and Use Cases

Verilog is widely used in digital circuit design for applications such as FPGA programming, ASIC design, and hardware verification due to its simplicity and C-like syntax, which accelerates development in industry settings. VHDL excels in aerospace, defense, and safety-critical systems where its strong typing and rigorous syntax enhance reliability and maintainability for complex embedded systems and communication protocols. Both languages support simulation and synthesis, but Verilog's dominance in commercial chip design contrasts with VHDL's preference in government and academic research environments.

Future Trends in HDL Development

Future trends in HDL development highlight increasing adoption of SystemVerilog for complex digital system design due to its enhanced verification capabilities and object-oriented features. Meanwhile, VHDL continues to evolve with updates targeting improved synthesis support and integration with high-level synthesis tools for FPGA and ASIC development. Emerging research emphasizes convergence between HDLs and high-level programming models to accelerate hardware-software co-design and enable more efficient validation and simulation workflows.

RTL (Register Transfer Level)

Verilog offers concise syntax and widespread industry adoption for RTL design, while VHDL provides strong typing and rigorous hardware abstraction, making each suited to different Register Transfer Level modeling preferences.

Synthesis

Verilog offers faster synthesis with simpler syntax favored in industry, while VHDL provides more rigorous type checking and strong hardware modeling suited for complex designs and reliability.

FPGA (Field Programmable Gate Array)

Verilog offers concise syntax and faster simulation for FPGA design, while VHDL provides strong type checking and better support for complex hardware modeling in FPGA development.

Testbench

Verilog testbenches offer simpler syntax and faster simulation for digital design verification, while VHDL testbenches provide stronger typing and more robust modularity for complex verification environments.

Simulation

Verilog offers faster simulation speeds and easier syntax for modeling digital circuits, while VHDL provides more detailed data types and stronger type checking for accurate and robust simulations.

IP Core (Intellectual Property Core)

Verilog offers faster simulation and is widely used for IP core development in digital design, while VHDL provides strong typing and better support for complex, reusable IP cores in safety-critical applications.

Behavioral Modeling

Behavioral modeling in Verilog emphasizes concise, event-driven syntax for describing hardware functionality, while VHDL offers more verbose, strongly typed constructs that enhance code readability and maintainability.

Structural Modeling

Verilog offers a more concise syntax for structural modeling with module instantiation and wire connections, while VHDL provides a strongly typed, verbose approach enabling precise hierarchical design through component declarations and port maps.

Netlist

Verilog and VHDL both generate netlists for hardware synthesis, but Verilog netlists are typically more concise and widely used in industry, while VHDL netlists offer stronger typing and are preferred for complex, safety-critical designs.

ASIC (Application Specific Integrated Circuit)

Verilog offers a concise syntax and widespread ASIC industry adoption, while VHDL provides strong typing and extensive design verification features, making them both essential for robust ASIC hardware description and synthesis.

Verilog vs VHDL Infographic

njnir.com

njnir.com