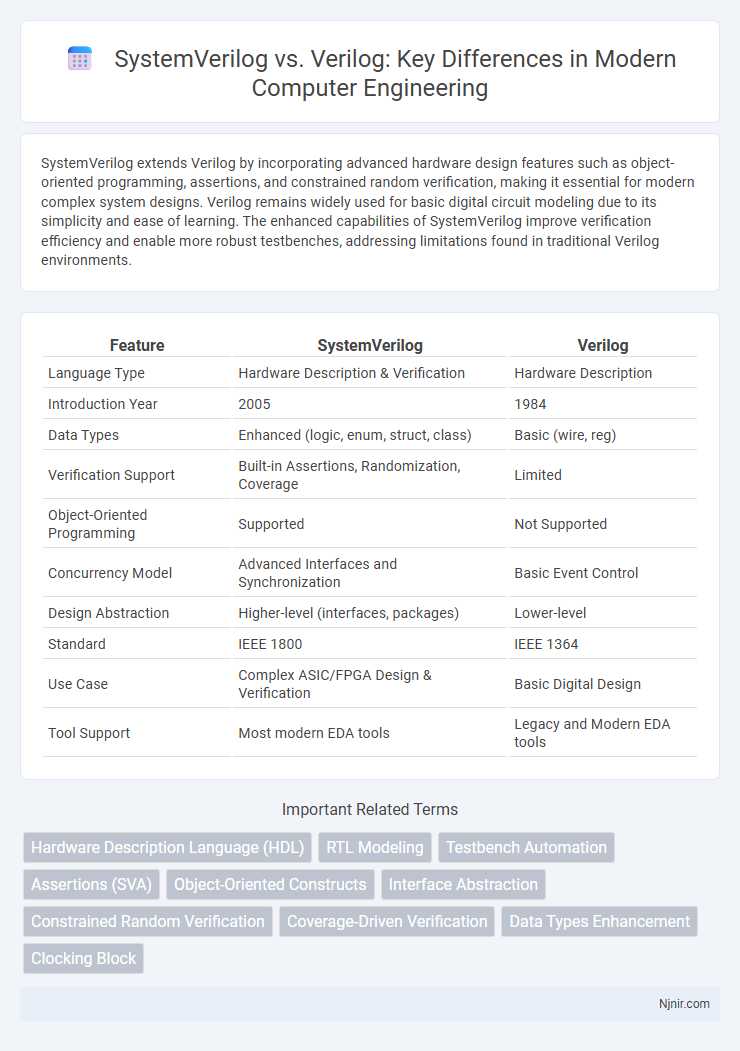

SystemVerilog extends Verilog by incorporating advanced hardware design features such as object-oriented programming, assertions, and constrained random verification, making it essential for modern complex system designs. Verilog remains widely used for basic digital circuit modeling due to its simplicity and ease of learning. The enhanced capabilities of SystemVerilog improve verification efficiency and enable more robust testbenches, addressing limitations found in traditional Verilog environments.

Table of Comparison

| Feature | SystemVerilog | Verilog |

|---|---|---|

| Language Type | Hardware Description & Verification | Hardware Description |

| Introduction Year | 2005 | 1984 |

| Data Types | Enhanced (logic, enum, struct, class) | Basic (wire, reg) |

| Verification Support | Built-in Assertions, Randomization, Coverage | Limited |

| Object-Oriented Programming | Supported | Not Supported |

| Concurrency Model | Advanced Interfaces and Synchronization | Basic Event Control |

| Design Abstraction | Higher-level (interfaces, packages) | Lower-level |

| Standard | IEEE 1800 | IEEE 1364 |

| Use Case | Complex ASIC/FPGA Design & Verification | Basic Digital Design |

| Tool Support | Most modern EDA tools | Legacy and Modern EDA tools |

Introduction to Verilog and SystemVerilog

Verilog is a hardware description language primarily used for modeling electronic systems and designing digital circuits, with a syntax resembling the C programming language. SystemVerilog extends Verilog by adding advanced features such as object-oriented programming, assertions, and improved verification capabilities, making it suitable for both design and verification tasks. The integration of SystemVerilog enhances productivity and efficiency in complex system development compared to traditional Verilog.

Key Differences Between Verilog and SystemVerilog

SystemVerilog extends Verilog by introducing advanced features such as object-oriented programming, assertions, and enhanced data types, enabling more efficient verification and design. Key differences include SystemVerilog's support for classes, interfaces, and randomization, which Verilog lacks, making SystemVerilog suitable for complex system-level modeling. Verilog primarily focuses on hardware description with simpler syntax, while SystemVerilog combines hardware design and verification capabilities in a unified language.

Enhanced Data Types in SystemVerilog

SystemVerilog introduces enhanced data types such as logic, bit, and byte that overcome Verilog's traditional reg and wire limitations, enabling more precise modeling and simulation. These enriched data types support packed and unpacked arrays, allowing multidimensional data structures and improving design readability and synthesis accuracy. SystemVerilog's strong typing and enhanced data abstraction capabilities significantly reduce design errors and enhance verification efficiency compared to Verilog.

Improvements in Design Modeling

SystemVerilog extends Verilog by introducing advanced design modeling capabilities such as enhanced data types, including packed structs and unions, which improve hardware representation precision. It adds object-oriented programming features like classes and inheritance, enabling more flexible and scalable testbenches and design abstractions. The interface construct in SystemVerilog simplifies complex module communication and promotes modular design practices, significantly enhancing overall hardware design modeling efficiency.

Verification Capabilities Comparison

SystemVerilog offers enhanced verification capabilities compared to Verilog, including built-in support for assertions, constrained random stimulus generation, and functional coverage, which streamline automated testbench creation and improve design validation. Its advanced object-oriented programming features enable reusable and modular testbench components, facilitating complex verification environments. Verilog lacks integrated verification constructs, often requiring external tools or libraries to achieve comparable testbench functionality.

Advanced Assertions and Functional Coverage

SystemVerilog enhances verification through advanced assertions that enable precise, temporal property checking and real-time error detection beyond Verilog's limited procedural assertions. It supports functional coverage metrics, including covergroups and coverpoints, to systematically quantify verification completeness and identify untested design scenarios. These features make SystemVerilog indispensable for rigorous, automated design verification in complex ASIC and FPGA projects.

Hardware Design: Synthesis and Simulation

SystemVerilog extends Verilog by providing advanced hardware design capabilities such as improved synthesis constructs and enhanced simulation features, enabling more precise modeling of complex digital systems. Its support for interfaces, user-defined types, and assertions improves design modularity and verification rigor, which Verilog lacks in standard form. The enhanced simulation capabilities in SystemVerilog allow faster identification of functional errors through constrained random testing and coverage-driven verification, making it a preferred choice for modern hardware design workflows.

Tool Support and Industry Adoption

SystemVerilog offers enhanced tool support compared to Verilog, with modern EDA tools providing advanced verification features such as assertions, constrained random testing, and coverage-driven verification. Major semiconductor companies widely adopt SystemVerilog for complex SoC designs due to its richer language constructs and improved simulation capabilities. Verilog remains prevalent for simpler designs and legacy projects, but SystemVerilog's industry adoption continues to grow, driven by evolving verification methodologies and toolchain optimizations.

Migration and Compatibility Considerations

SystemVerilog extends Verilog by adding advanced features such as object-oriented programming, assertions, and enhanced data types, which require careful migration planning to ensure compatibility with existing Verilog codebases. Compatibility considerations include verifying tool support for SystemVerilog constructs, updating testbenches, and refactoring legacy Verilog code to leverage SystemVerilog's improved verification capabilities while maintaining functional correctness. Migrating incrementally by integrating SystemVerilog modules alongside Verilog allows for a smoother transition and minimizes risk during hardware design verification.

Choosing the Right HDL for Your Project

SystemVerilog offers advanced features such as object-oriented programming, assertions, and enhanced testbench capabilities that make it ideal for complex system design and verification compared to Verilog's simpler syntax and limited constructs. Choosing SystemVerilog accelerates verification processes for large-scale ASIC and FPGA projects by enabling more comprehensive testbenches and improved debugging tools. Smaller projects or those with legacy constraints may benefit from Verilog's straightforward approach and broader tool support, balancing development speed with resource availability.

Hardware Description Language (HDL)

SystemVerilog enhances Verilog by integrating advanced Hardware Description Language (HDL) features like object-oriented programming, better verification capabilities, and improved design modeling for complex digital systems.

RTL Modeling

SystemVerilog enhances RTL modeling compared to Verilog by offering advanced features such as object-oriented programming, enhanced data types, improved concurrency control, and built-in assertion support, enabling more efficient and robust hardware design.

Testbench Automation

SystemVerilog enhances testbench automation with advanced features like constrained random stimulus generation, functional coverage, and assertions, surpassing the capabilities of traditional Verilog.

Assertions (SVA)

SystemVerilog Assertions (SVA) provide advanced temporal and functional verification capabilities beyond traditional Verilog, enabling more precise design validation and formal verification.

Object-Oriented Constructs

SystemVerilog enhances hardware design and verification by integrating object-oriented constructs like classes, inheritance, and polymorphism, which are absent in traditional Verilog.

Interface Abstraction

SystemVerilog enhances interface abstraction over Verilog by introducing interface constructs that encapsulate signal groups and synchronization logic, promoting modular design and reducing code complexity.

Constrained Random Verification

SystemVerilog enhances Constrained Random Verification by integrating advanced randomization methods, constraints, and coverage features absent in Verilog, enabling more efficient and thorough functional verification.

Coverage-Driven Verification

SystemVerilog enhances Coverage-Driven Verification by providing advanced functional coverage constructs, seamless integration with UVM, and comprehensive coverage metrics not available in traditional Verilog.

Data Types Enhancement

SystemVerilog enhances Verilog by introducing robust data types such as logic, bit, byte, enum, and struct, enabling improved modeling precision and simulation accuracy in hardware design.

Clocking Block

SystemVerilog's clocking block enhances timing control and synchronization in testbenches, offering more precise signal sampling and driving compared to Verilog's traditional approach.

SystemVerilog vs Verilog Infographic

njnir.com

njnir.com